# **AMD5<sub>K</sub>86<sup>™</sup> Processor**

**Technical Reference Manual**

#### © 1996 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to any implied warranty of merchantability or fitness for a particular purpose.

AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included herein.

Trademarks:

AMD, the AMD logo and combinations thereof,  $AMD5_{K}86$ , and K86 are trademarks, and Am386 and Am486 are registered trademarks of Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks and Windows NT is a trademark of Microsoft.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## Contents

| 1 | Overview          |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-1                  |

|---|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|   | 1.1               | Features                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-2                  |

| 2 | Internal Archited | ıre                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-1                  |

|   | 2.1               | Prefetch and Predecode                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-3                  |

|   | 2.2               | Execution Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

|   | 2.3               | Cache Organization and Management                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

|   |                   | <ul> <li>2.3.1 Instruction Cache</li> <li>2.3.2 Data Cache</li> <li>2.3.3 Cache Tags</li> <li>2.3.4 Cache-Line Fills</li> <li>2.3.5 Cache Coherency</li> <li>2.3.6 Snooping</li> <li>2.3.6 Snooping</li> <li>2.3.7 Buffers</li> <li>2.3.7 Buffers</li> <li>2.3.7 Buffers</li> <li>2.3.7 Prefetch Cache</li> <li>2.3.8 Store Buffer</li> <li>2.3.9 Replacement and Invalidation Writeback Buffer</li> <li>2.3.9 Snoop Writeback Buffer</li> </ul> |                      |

|   | 2.4               | Memory Management Unit (MMU)2.4.1Storage Model2.4.2Read/Write Reordering2.4.3Segmentation2.4.4Paging and the TLBs                                                                                                                                                                                                                                                                                                                                | 2-26<br>2-27<br>2-27 |

## **3** Software Environment and Extensions

| 3-1 |  |

|-----|--|

|-----|--|

| 3.1           | Control Register 4 (CR4) Extensions3-23.1.1Machine-Check Exceptions3-43.1.24-Mbyte Pages3-53.1.3Global Pages3-93.1.4Virtual-8086 Mode Extensions (VME)3-12Interrupt Redirection in Virtual-8086 Mode Without3-12VME Extensions3-12Hardware Interrupts and the VIF and VIP Extensions3-13Software Interrupts and the Interrupt Redirection3-21Bitmap (IRB) Extension3-213.1.5Protected Virtual Interrupt (PVI) Extensions3-24 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2           | Model-Specific Registers (MSRs)3-253.2.1Machine-Check Address Register (MCAR)3-253.2.2Machine-Check Type Register (MCTR)3-263.2.3Time Stamp Counter (TSC)3-273.2.4Array Access Register (AAR)3-273.2.5Hardware Configuration Register (HWCR)3-28                                                                                                                                                                             |

| 3.3           | New Instructions         3-28           3.3.1         CPUID         3-29           3.3.2         CMPXCHG8B         3-32           3.3.3         MOV to and from CR4         3-33           3.3.4         RDTSC         3-34           3.3.5         RDMSR and WRMSR         3-35           3.3.6         RSM         3-37           3.3.7         Illegal Instruction (Reserved Opcode)         3-38                         |

| 4 Performance | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.1           | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                         |

| 4.2           | Dispatch and Execution Timing4-54.2.1Notation4-54.2.2Integer Instructions4-84.2.3Integer Dot Product Example4-174.2.4Floating-Point Instructions4-19                                                                                                                                                                                                                                                                         |

### **5 Bus Interface**

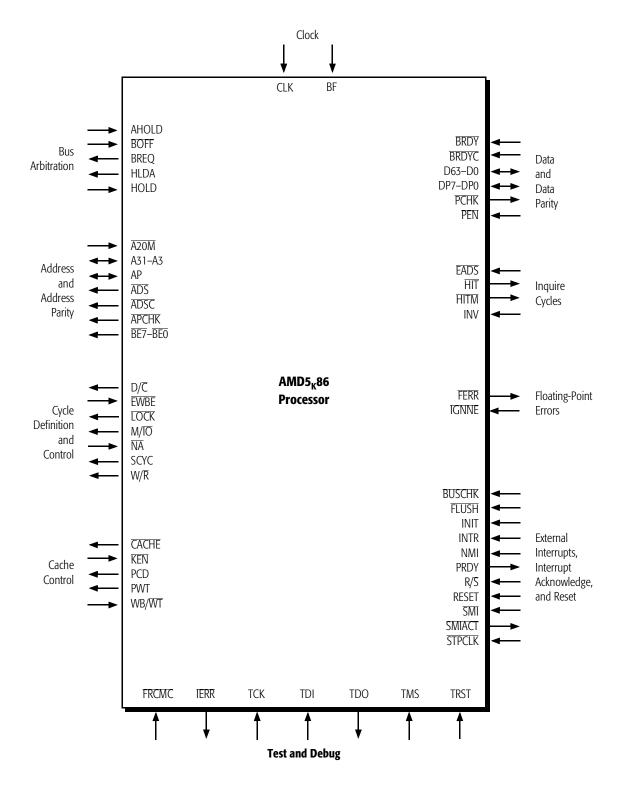

| 51  | Signa          | l Overview                                                   | 5-2    |

|-----|----------------|--------------------------------------------------------------|--------|

| 5.1 | 5.1.1          | Signal Characteristics                                       |        |

|     | 5.1.2          | Conditions for Driving and Sampling Signals                  |        |

|     | 5.1.3          | External Interrupts                                          |        |

|     | 5.1.4          | Bus Signal Compatibility with Pentium Processor              |        |

| = 2 |                |                                                              |        |

| 5.2 | •              | Descriptions                                                 |        |

|     | 5.2.1          | A20M (Address Bit 20 Mask)                                   |        |

|     | 5.2.2          | A31–A3 (Address Bus)                                         |        |

|     | 5.2.3          | ADS (Address Strobe)                                         |        |

|     | 5.2.4<br>5.2.5 | ADSC (Address Strobe Copy)         AUOL D (Address Hold)     |        |

|     | 5.2.5<br>5.2.6 | AHOLD (Address Hold)                                         |        |

|     | 5.2.6<br>5.2.7 | AP (Address Parity)                                          |        |

|     | 5.2.7<br>5.2.8 | APCHK (Address Parity Check)         RE7_RE0 (Brits Enclose) |        |

|     | 5.2.8<br>5.2.9 | BE7–BE0 (Byte Enables)                                       |        |

|     |                | BF (Bus Frequency)                                           |        |

|     |                | BOFF (Backoff)          BRDY (Burst Ready)                   |        |

|     |                | RDYC (Burst Ready)                                           |        |

|     |                | BREQ (Bus Request)                                           |        |

|     |                | BUSCHK (Bus Check)                                           |        |

|     |                | CACHE (Cacheable Access)                                     |        |

|     |                | CLK (Bus Clock)                                              |        |

|     |                | D/C (Data or Code)                                           |        |

|     |                | D63–D0 (Data Bus)                                            |        |

|     |                | DP7–DP0 (Data Parity)                                        |        |

|     |                | EADS (External Address Strobe)                               |        |

|     |                | <b>EWBE</b> (External Write Buffer Empty)                    |        |

|     |                | FERR (Floating-Point Error)                                  |        |

|     |                | FLUSH (Cache Flush)                                          |        |

|     |                | <b>FRCMC</b> (Functional-Redundancy Check Master/Checker)    |        |

|     |                | HIT (Inquire-Cycle Hit)                                      |        |

|     |                | HITM (Inquire Cycle Hit To Modified Line)                    |        |

|     |                | HLDA (Bus-Hold Acknowledge)                                  |        |

|     |                | HOLD (Bus-Hold Request)                                      |        |

|     |                | IERR (Internal Error)                                        |        |

|     |                | IGNNE (Ignore Numeric Error)                                 |        |

|     |                | INIT (Initialization)                                        |        |

|     |                | INTR (Maskable Interrupt)                                    |        |

|     |                | INV (Invalidate Cache Line)                                  |        |

|     |                | KEN (External Cache Enable)                                  |        |

|     | 5.2.35         | LOCK (Bus Lock)                                              | . 5-92 |

|     |                | M/IO (Memory or I/O)                                         |        |

|     |                | NA (Next Address)                                            |        |

|     |                | NMI (Non-Maskable Interrupt)                                 |        |

|     |                | PCD (Page Cache Disable)                                     |        |

|     |                |                                                              |        |

| $ [7] \Lambda() D(UIIV (Dominus (Modera)) $                                                                                                                                                                                                                                                                                                      | F 102                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2.40 $\overrightarrow{\text{PCHK}}$ (Parity Status)                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                     |

| 5.2.41 PEN (Parity Enable)                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                     |

| 5.2.42 PRDY (Probe Ready)                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |

| 5.2.43 PWT (Page Writethrough)                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                     |

| 5.2.44 R/ $\overline{S}$ (Run or Stop)                                                                                                                                                                                                                                                                                                           | 5-108                                                                                                                                                                                                                                               |

| 5.2.45 RESET (Reset)                                                                                                                                                                                                                                                                                                                             | 5-110                                                                                                                                                                                                                                               |

| 5.2.46 SCYC (Split Cycle)                                                                                                                                                                                                                                                                                                                        | 5-115                                                                                                                                                                                                                                               |

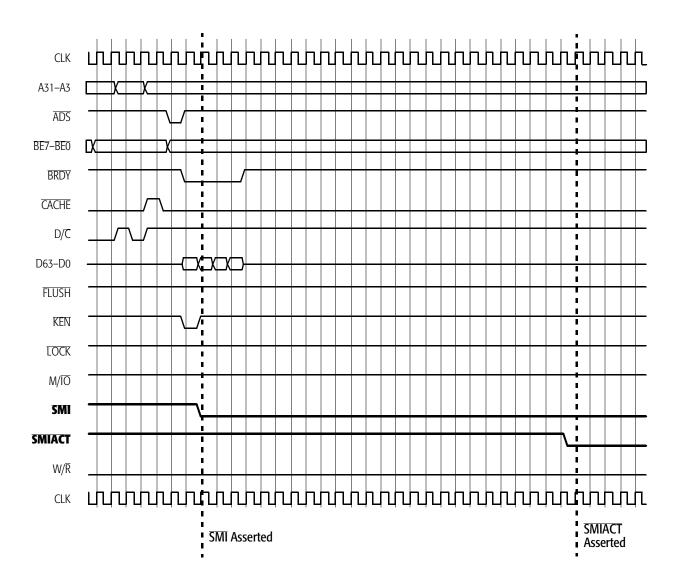

| 5.2.47 SMI (System Management Interrupt)                                                                                                                                                                                                                                                                                                         | 5-117                                                                                                                                                                                                                                               |

| 5.2.48 SMIACT (System Management Interrupt Active)                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                     |

| 5.2.49 <b>STPCLK</b> (Stop Clock)                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                     |

| 5.2.50 TCK (Test Clock)                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     |

| 5.2.51 TDI (Test Data Input)                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     |

| 5.2.52 TDO (Test Data Mput)                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                     |

| 5.2.53 TMS (Test Mode Select)                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                     |

| 5.2.54 <b>TRST</b> (Test Reset)                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                     |

| 5.2.55 W/ $\overline{\mathbf{R}}$ (Write or Read)                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                     |

| 5.2.56 WB/WT (Writeback or Writethrough)                                                                                                                                                                                                                                                                                                         | 5-134                                                                                                                                                                                                                                               |

| 5.3 Bus Cycle Overview                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                     |

| 5.3.1 Cycle Definitions                                                                                                                                                                                                                                                                                                                          | 5-137                                                                                                                                                                                                                                               |

| 5.3.2 Addressing                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                     |

| 5.3.3 Alignment                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                     |

| 0                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                     |

| 5.3.4 Bus Speed and Typical DRAM Timing                                                                                                                                                                                                                                                                                                          | 5-140                                                                                                                                                                                                                                               |

| <ul><li>5.3.4 Bus Speed and Typical DRAM Timing</li><li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                     | 5-140<br>5-140                                                                                                                                                                                                                                      |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> </ul>                                                                                                                                                                                                                    | 5-140<br>5-140<br><b>5-141</b>                                                                                                                                                                                                                      |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> <li>5.4.1 Timing Diagrams</li> </ul>                                                                                                                                                                                     | 5-140<br>5-140<br>5-141<br>5-141                                                                                                                                                                                                                    |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> </ul>                                                                                                                                                                                                                    | 5-140<br>5-140<br>5-141<br>5-141                                                                                                                                                                                                                    |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> <li>5.4.1 Timing Diagrams</li> </ul>                                                                                                                                                                                     | 5-140<br>5-140<br>5-141<br>5-141<br>5-142                                                                                                                                                                                                           |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> <li>5.4.1 Timing Diagrams</li> <li>5.4.2 Single-Transfer Reads and Writes</li> </ul>                                                                                                                                     | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>5-142                                                                                                                                                                                                  |

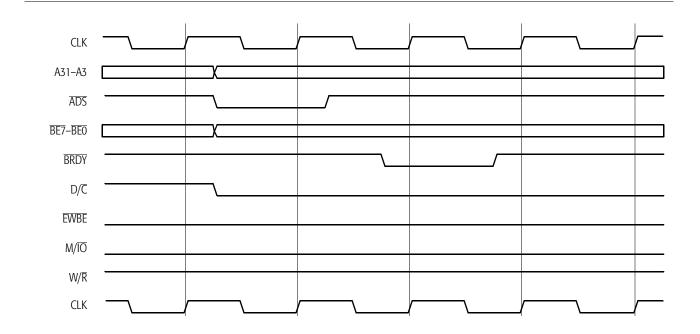

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> <li>5.4.1 Timing Diagrams</li> <li>5.4.2 Single-Transfer Reads and Writes</li> <li>Single-Transfer Memory Read and Write</li> </ul>                                                                                      | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>5-142<br>gnal 5-145                                                                                                                                                                                    |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> <li>5.4.1 Timing Diagrams</li> <li>5.4.2 Single-Transfer Reads and Writes</li> <li>Single-Transfer Memory Read and Write</li> <li>Single-Transfer Memory Write Delayed by EWBE Si</li> <li>I/O Read and Write</li> </ul> | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>5-142<br>gnal 5-145<br>5-147                                                                                                                                                                           |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>5-142<br>gnal 5-145<br>5-147<br>rs 5-148                                                                                                                                                               |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-142<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-148<br>5-150                                                                                                                                                 |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-148<br>5-150<br>5-150                                                                                                                                        |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-142<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-148<br>5-150<br>5-150                                                                                                                            |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-148<br>5-150<br>5-150<br>5-154<br>5-157                                                                                                                      |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-148<br>5-150<br>5-150<br>5-154<br>5-157<br>5-158                                                                                                             |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-150<br>5-150<br>5-154<br>5-158<br>t 5-158<br>t 5-160                                                                               |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-150<br>5-150<br>5-154<br>5-157<br>5-158<br>Line 5-160<br>5-161                                                                     |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li></ul>                                                                                                                                                                                                                                                                                       | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-147<br>rs 5-150<br>5-150<br>5-154<br>5-157<br>5-158<br>Line 5-160<br>5-161<br>5-163                                                              |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li></ul>                                                                                                                                                                                                                                                                                       | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-148<br>5-150<br>5-150<br>5-154<br>5-158<br>Line 5-160<br>5-163<br>5-163<br>5-165                                                                 |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-147<br>rs 5-147<br>rs 5-147<br>rs 5-150<br>5-150<br>5-154<br>5-158<br>Line 5-160<br>5-163<br>5-165<br>Line . 5-167                                             |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li></ul>                                                                                                                                                                                                                                                   | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-150<br>5-150<br>5-150<br>5-154<br>5-157<br>5-161<br>5-163<br>5-165<br>Line 5-167<br>5-169                                          |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> <li>5.4.1 Timing Diagrams</li></ul>                                                                                                                                                                                      | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-147<br>rs 5-150<br>5-150<br>5-150<br>5-154<br>5-157<br>5-161<br>5-163<br>5-165<br>Line 5-167<br>5-169<br>5-170                                   |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li></ul>                                                                                                                                                                                                                                                                                       | 5-140<br>5-140<br>5-141<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-145<br>5-147<br>rs 5-147<br>rs 5-150<br>5-150<br>5-150<br>5-154<br>5-158<br>Line 5-160<br>5-163<br>5-163<br>5-165<br>Line . 5-167<br>5-170<br>5-170                 |

| <ul> <li>5.3.4 Bus Speed and Typical DRAM Timing</li> <li>5.3.5 Bus-Cycle Priorities</li> <li>5.4 Bus Cycle Timing</li> <li>5.4.1 Timing Diagrams</li></ul>                                                                                                                                                                                      | 5-140<br>5-140<br>5-141<br>5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-142<br>gnal 5-142<br>s 5-142<br>gnal 5-147<br>rs 5-150<br>5-150<br>5-150<br>5-158<br>Line 5-160<br>5-163<br>5-163<br>5-165<br>Line 5-167<br>5-169<br>5-170<br>5-170<br>5-170 |

|       | Interrupt Acknowledge Operation                  | 5-176 |

|-------|--------------------------------------------------|-------|

| 5.4.6 | Special Bus Cycles                               | 5-181 |

|       | Basic Special Bus Cycle                          | 5-182 |

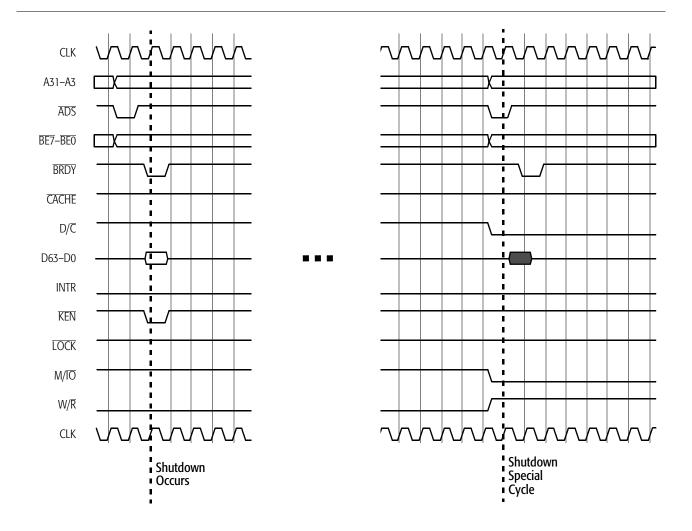

|       | Shutdown Cycle                                   | 5-183 |

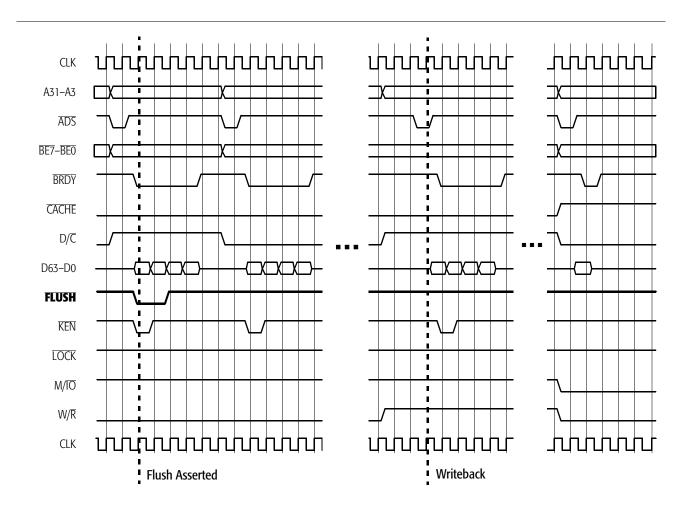

|       | FLUSH-Acknowledge Cycle                          | 5-184 |

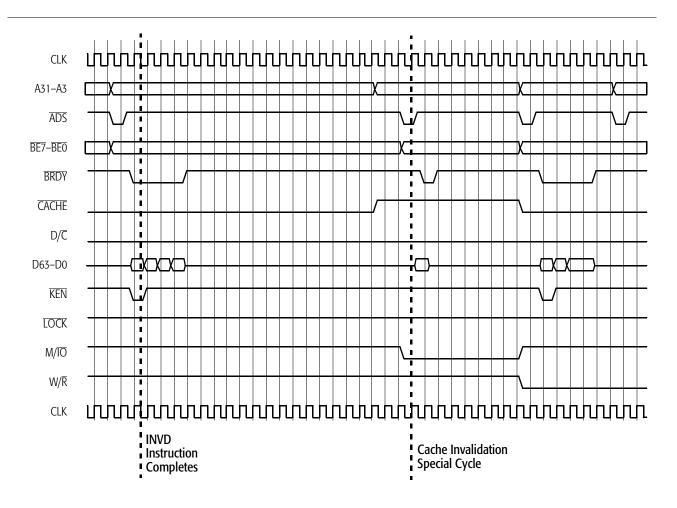

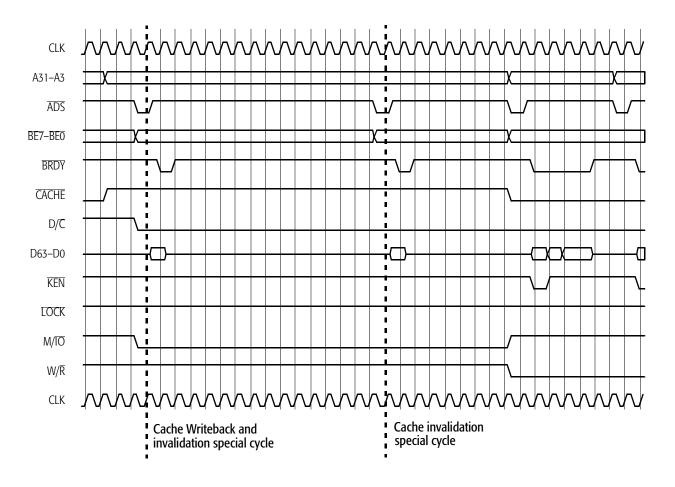

|       | Cache-Invalidation Cycle (INVD Instruction)      | 5-185 |

|       | Cache-Writeback and Invalidation Cycle           |       |

|       | (WBINVD Instruction)                             | 5-186 |

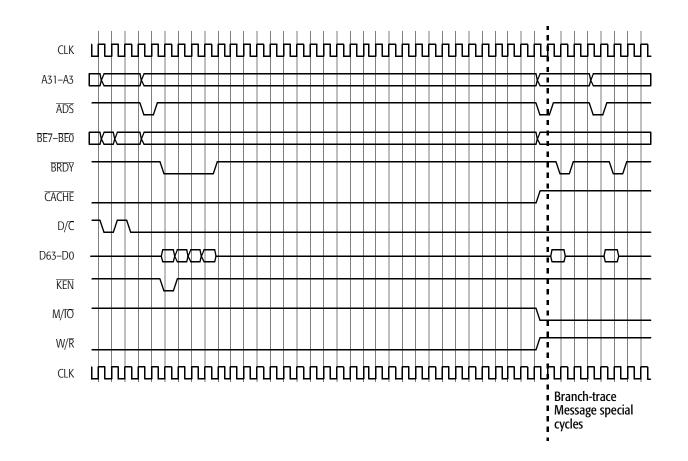

|       | Branch-Trace Message Cycles                      | 5-188 |

| 5.4.7 | Mode Transitions, Reset, and Testing             | 5-190 |

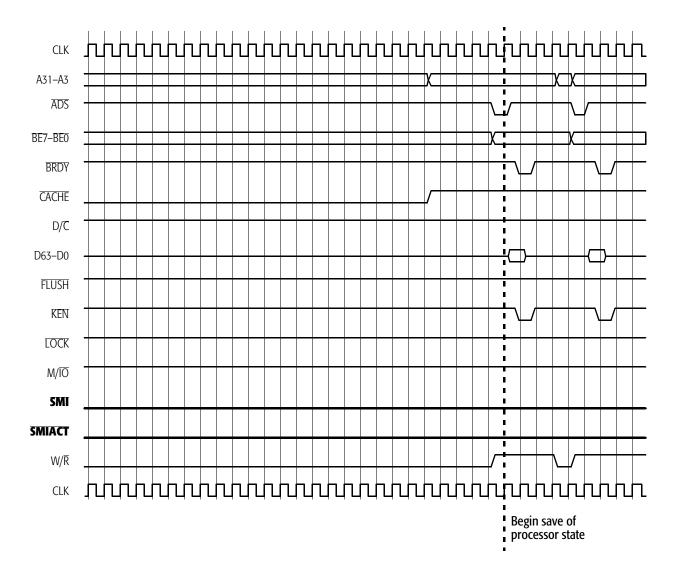

|       | Transition from Normal Execution to SMM          | 5-190 |

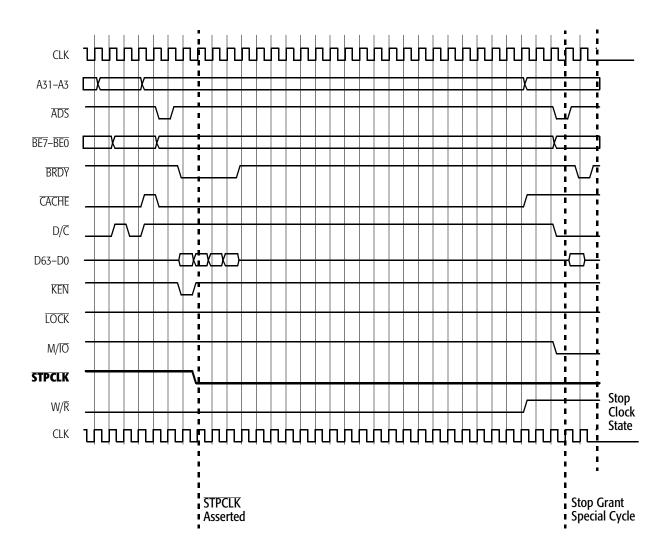

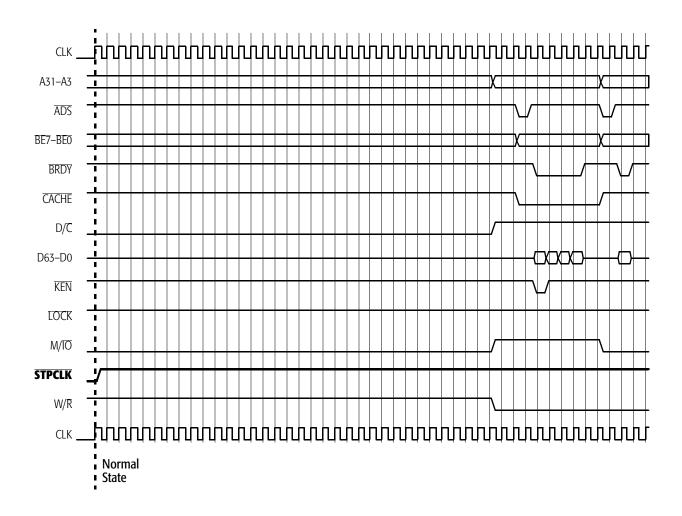

|       | Stop-Grant and Stop-Clock States                 | 5-193 |

|       | INIT-Initiated Transition from Protected Mode to |       |

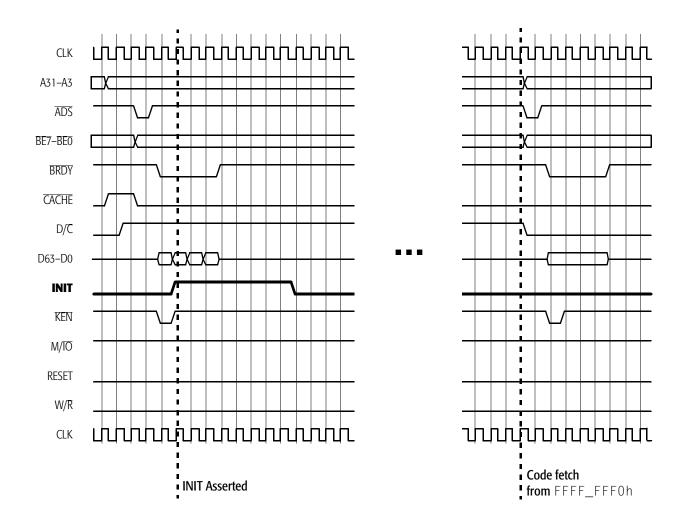

|       | Real Mode                                        | 5-196 |

|       |                                                  |       |

## 6 System Design

### 6-1

| 6.1 | Mem   | ory                                              |

|-----|-------|--------------------------------------------------|

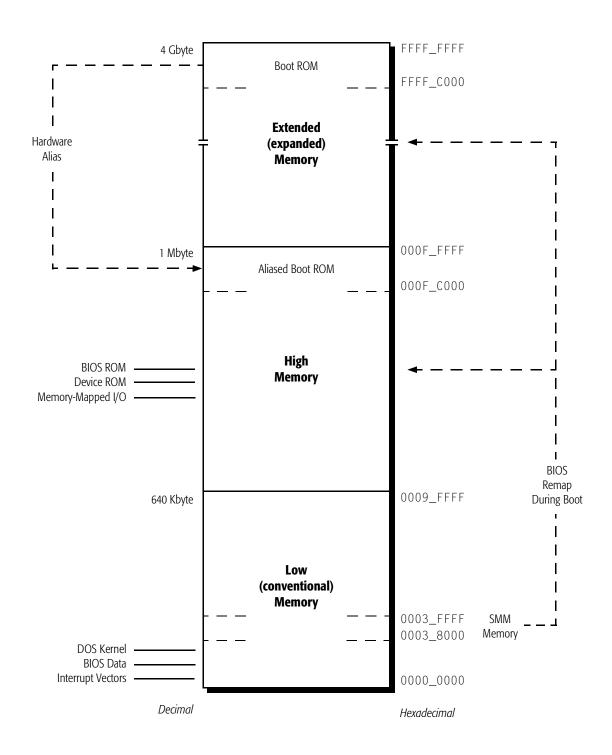

|     | 6.1.1 | Memory Map 6-2                                   |

|     | 6.1.2 | Memory-Decoder Aliasing of Boot ROM Space 6-4    |

|     | 6.1.3 | Cacheable and Noncacheable Address Spaces        |

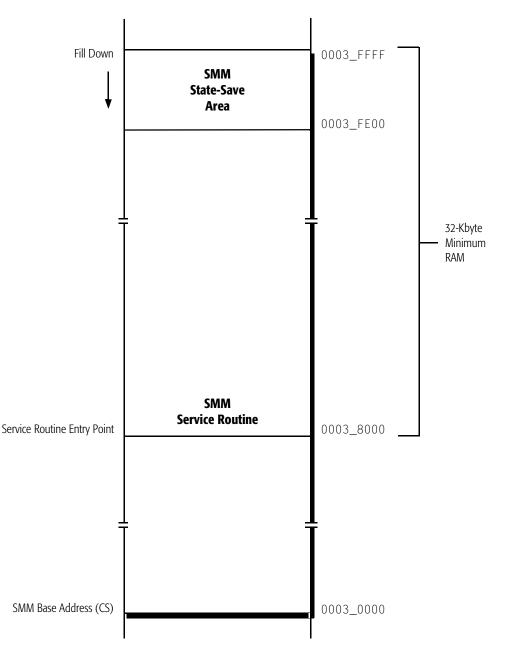

|     | 6.1.4 | SMM Memory Space and Cacheability 6-5            |

| 6.2 | Cach  | e                                                |

|     | 6.2.1 | L2 Cache                                         |

|     | 6.2.2 | Cacheability and Cache-State Control 6-9         |

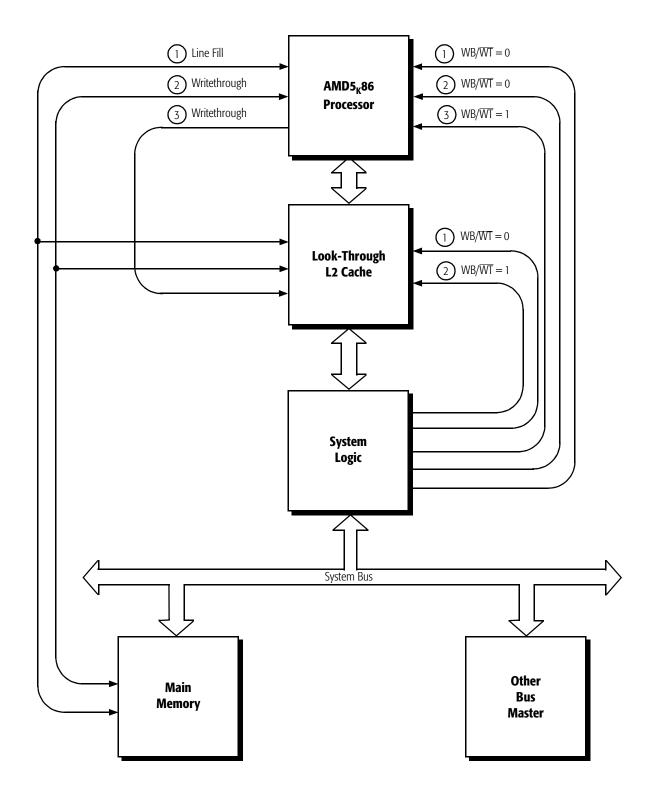

|     | 6.2.3 | Writethrough vs. Writeback Coherency States 6-10 |

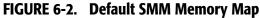

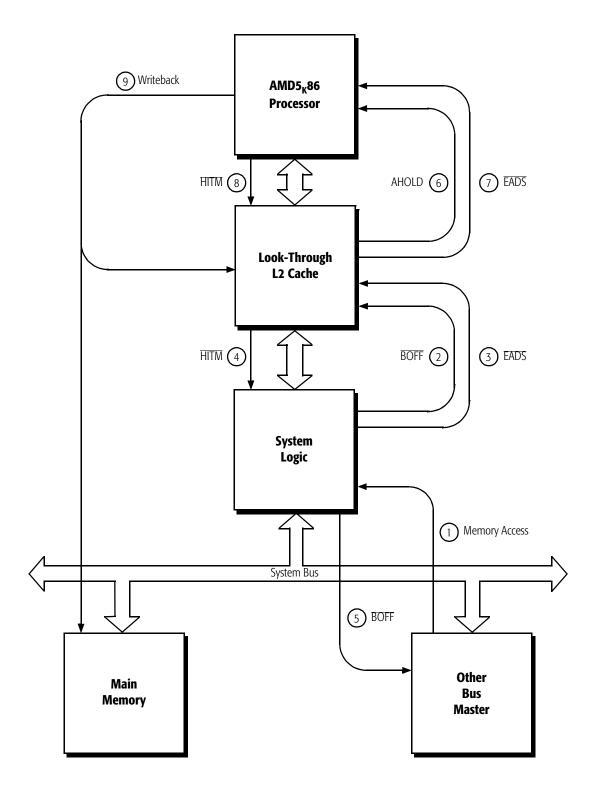

|     | 6.2.4 | Inquire Cycles 6-12                              |

|     | 6.2.5 | Bus Arbitration for Inquire Cycles 6-14          |

|     |       | BOFF Arbitration                                 |

|     |       | AHOLD Arbitration6-17                            |

|     |       | HOLD Arbitration 6-19                            |

|     | 6.2.6 | Write-Once Protocol 6-19                         |

|     | 6.2.7 | Cache Invalidations 6-22                         |

|     | 6.2.8 | A20M Masking of Cache Accesses6-22               |

| 6.3 | Syste | m Management Mode (SMM)6-23                      |

|     | 6.3.1 | Operating Mode and Default Register Values 6-24  |

|     | 6.3.2 | SMM State-Save Area 6-25                         |

|     | 6.3.3 | SMM Revision Identifier 6-28                     |

|     | 6.3.4 | SMM Base Address 6-28                            |

|     | 6.3.5 | Halt Restart Slot6-30                            |

|     | 6.3.6 | I/O Trap Dword                                   |

|     | 6.3.7 | I/O Trap Restart Slot 6-31                       |

|     | 6.3.8 | Exceptions and Interrupts in SMM                 |

|     | 6.3.9 | SMM Compatibility with Pentium Processor 6-33    |

7 Test and

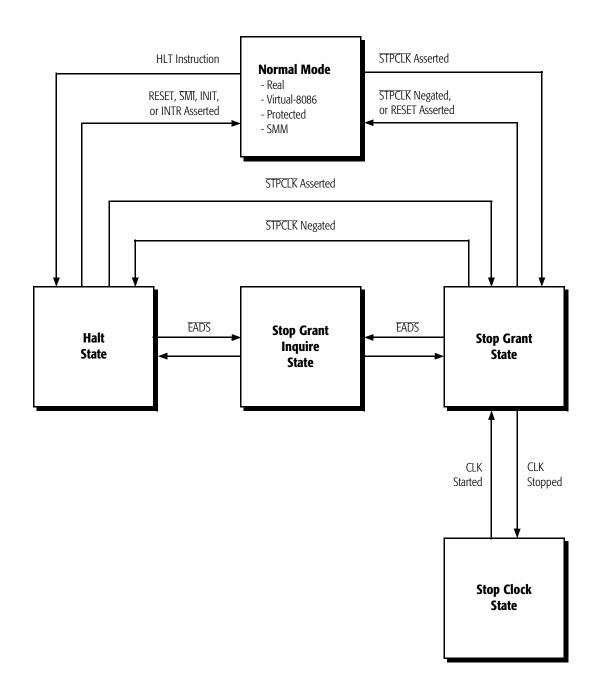

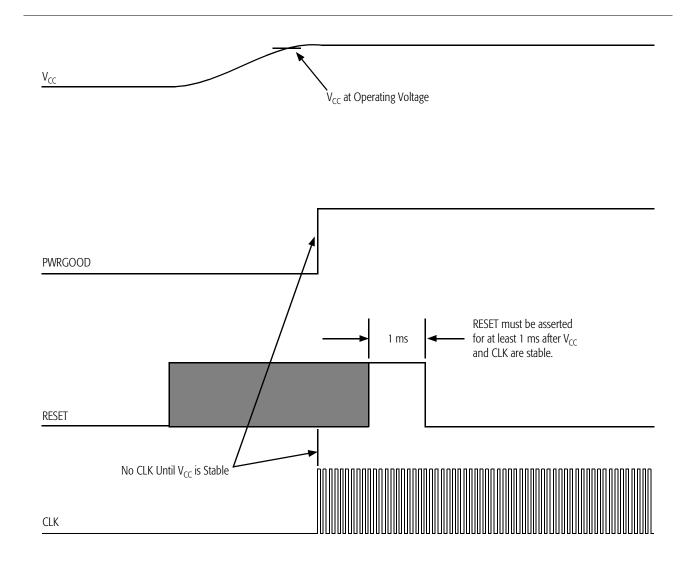

|     | 6.4 | Clock Control6-336.4.1 State Transitions6-346.4.2 Halt State6-346.4.3 Stop Grant State6-376.4.4 Stop Grant Inquire State6-376.4.5 Stop Clock State6-386.4.6 Clock Control Compatibility with Pentium Processor6-38 |

|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 6.5 | Power and Ground Design                                                                                                                                                                                            |

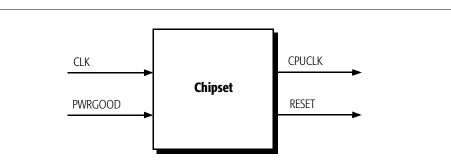

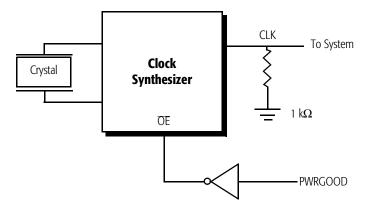

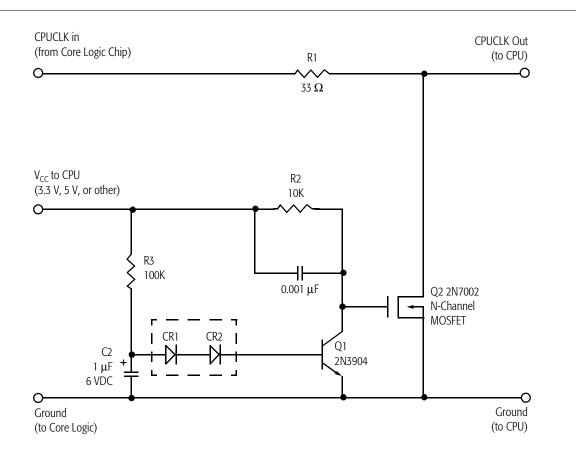

|     | 6.6 | Clock Design         6-40           6.6.1         Noise Reduction         6-43                                                                                                                                     |

|     | 6.7 | Thermal Design                                                                                                                                                                                                     |

|     | 6.8 | Design Support and Peripheral Products6-45                                                                                                                                                                         |

| Deb | ug  | 7-1                                                                                                                                                                                                                |

|     | 7.1 | Hardware Configuration Register (HWCR)7-3                                                                                                                                                                          |

|     | 7.2 | Built-In Self Test (BIST)         7-5           7.2.1         Normal BIST         7-5           7.2.2         Test Access Port (TAP) BIST         7-6                                                              |

|     | 7.3 | Output-Float Test7-7                                                                                                                                                                                               |

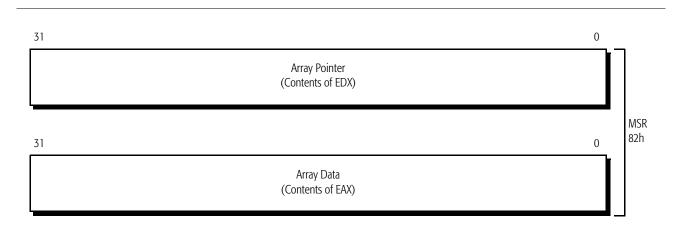

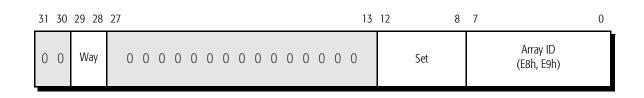

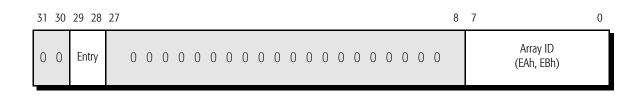

|     | 7.4 | Cache and TLB Testing7-77.4.1Array Access Register (AAR)7-87.4.2Array Pointer7-97.4.3Array Test Data7-10                                                                                                           |

|     | 7.5 | Debug Registers7-167.5.1Standard Debug Functions7-167.5.2I/O Breakpoint Extension7-167.5.3Debug Compatibility with Pentium Processor7-17                                                                           |

|     | 7.6 | Branch Tracing                                                                                                                                                                                                     |

|     | 7.7 | Functional-Redundancy Checking7-18                                                                                                                                                                                 |

|     | 7.8 | Boundary-Scan Test Access Port (TAP)7-197.8.1Device Identification Register7-217.8.2Public Instructions7-22                                                                                                        |

|     | 7.9 | Hardware Debug Tool (HDT)7-23                                                                                                                                                                                      |

| Appendix A | Compa       | tibility With the Pentium and 486 Processors                                                                                                                                                                                                                                                                                                                                      | <b>A-1</b>                      |

|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|            | <b>A.1</b>  | Bus Signals    A      A.1.1    Signal Comparison                                                                                                                                                                                                                                                                                                                                  |                                 |

|            | A.2         | Bus Interface       A         A.2.1       Updates to Descriptor Accessed and TSS Busy Bits       A         A.2.2       Locked and Unlocked CMPXCHG8B Operation       A         A.2.3       Bus Cycle Order of Misaligned Memory and I/O Cycles       A         A.2.4       Halt Cycle after FLUSH       A         A.2.5       Selectable Drive Strengths on Output Driver       A | A-5<br>A-5<br>A-6<br>A-6<br>A-6 |

|            | A.3         | Bus Mastering Operations (including Snooping)       A         A.3.1       AHOLD Snoop to Linefill Buffer Prior to or Coincident with the Establishment of the Cacheability of the Line       A         Comments       Comments       Comments                                                                                                                                     | A-8                             |

|            |             | <ul> <li>A.3.2 BOFF Asserted before Snoop to Linefill Buffer and after the Cacheability of the Line is Established</li> <li>A.3.3 Snoop Before Write Hit to ICACHE Appears on Bus</li> <li>A.3.4 Invalidations during a FLUSH/WBINVD</li> <li>A.3.5 Cache Line Ownership</li> <li>A.3.6 Write Hit to a Shared Line in the DCACHE</li> </ul>                                       | A-9<br>A-9<br>A-9<br>A-9        |

|            | <b>A.4</b>  | Memory Management       A         A.4.1 Speculative TLB Refills       A         A.4.2 Page Fault Encountered by a Load/Store Type of Instruction       A                                                                                                                                                                                                                          | -11                             |

|            | <b>A.5</b>  | Power Saving FeaturesAA.5.1STPCLK in Halt StateA.5.2STPCLK Pulse does not Guarantee That One                                                                                                                                                                                                                                                                                      | <b>-12</b><br>-12               |

|            |             | Instruction Executes       A         A.5.3       Simultaneous I/O SMI Trap and Debug Breakpoint Trap       A         A.5.4       SMM Save Area       A         A.5.5       NMI Recognition during SMM       A         Comment       A                                                                                                                                             | -12<br>-12<br>-13               |

|            | <b>A.6</b>  | <b>Exceptions</b> AA.6.1Limit Faults on an Invalid InstructionAA.6.2Task SwitchA                                                                                                                                                                                                                                                                                                  | -14                             |

|            | <b>A.</b> 7 | DebugAA.7.1Proprietary Branch Trace MessagesAA.7.2Multiple Debug Breakpoint MatchesAA.7.3Simultaneous Debug Trap and Debug FaultA                                                                                                                                                                                                                                                 | -15<br>-15                      |

## **List of Figures**

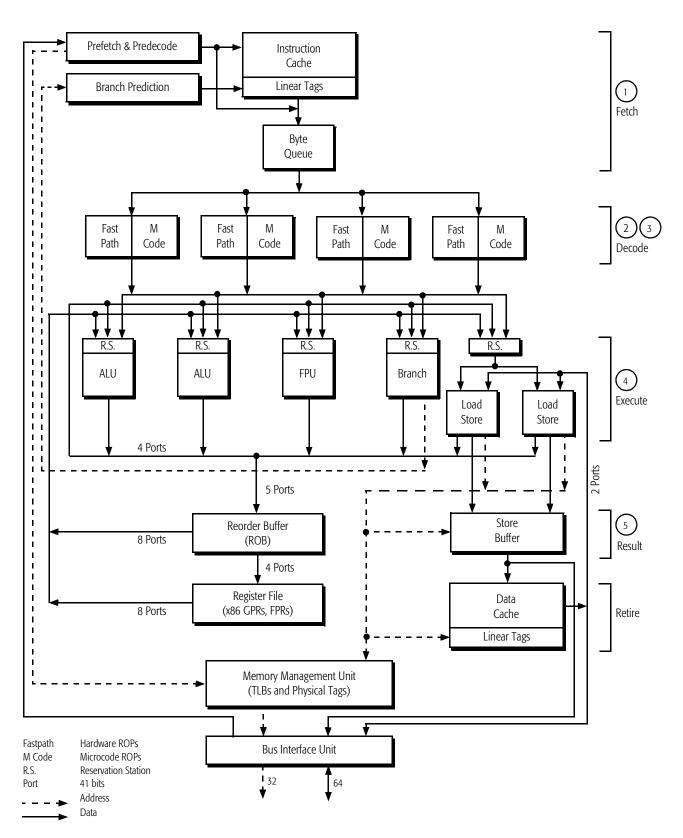

| FIGURE 2- | -1. | Internal Architecture, with Pipeline Stage    | 2-2   |

|-----------|-----|-----------------------------------------------|-------|

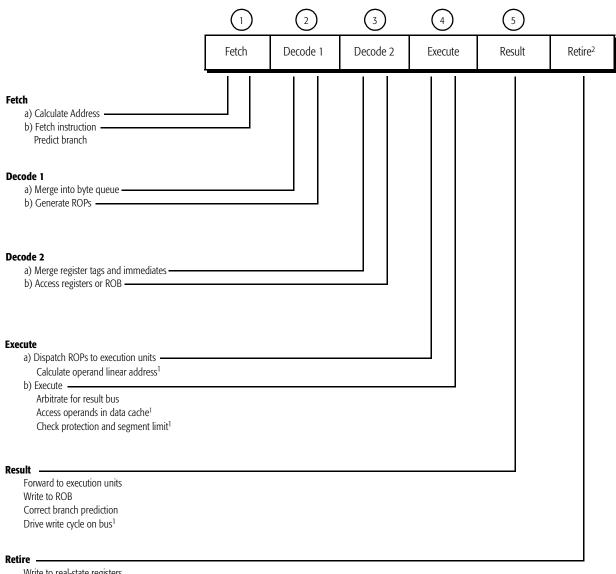

| FIGURE 2- | -2. | Pipeline Stage Functions                      | 2-5   |

| FIGURE 3- | -1. | Control Register 4 (CR4)                      | 3-2   |

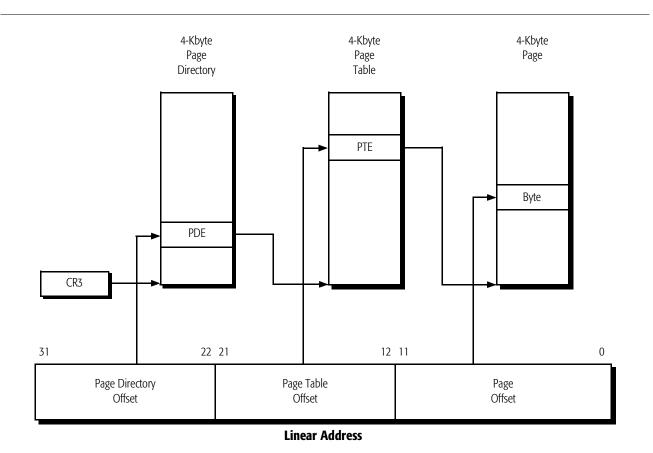

| FIGURE 3- | -2. | 4-Kbyte Paging Mechanism                      | 3-5   |

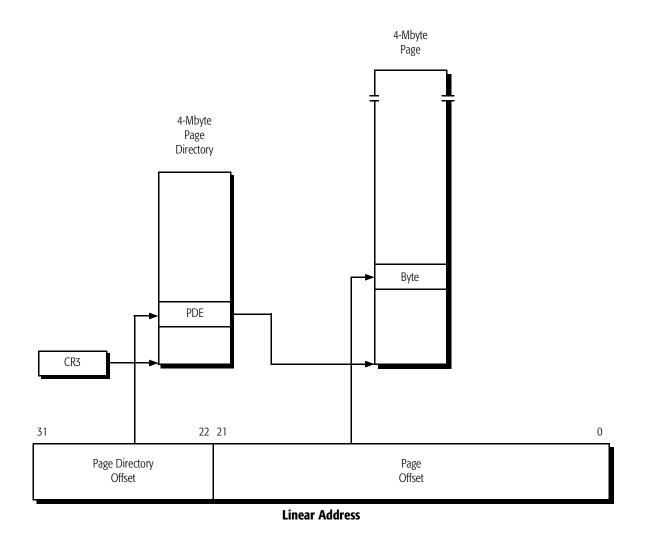

| FIGURE 3  |     | 4-Mbyte Paging Mechanism                      |       |

| FIGURE 3  |     | Page-Directory Entry (PDE)                    |       |

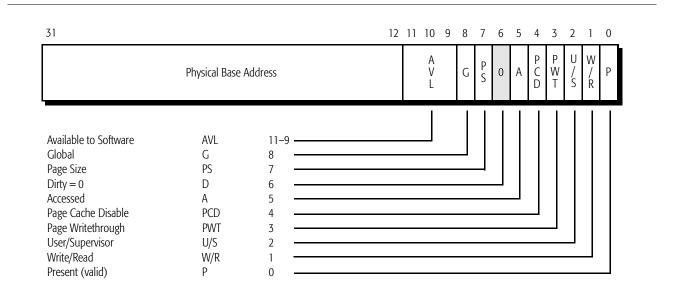

| FIGURE 3- |     | Page-Table Entry (PTE)                        |       |

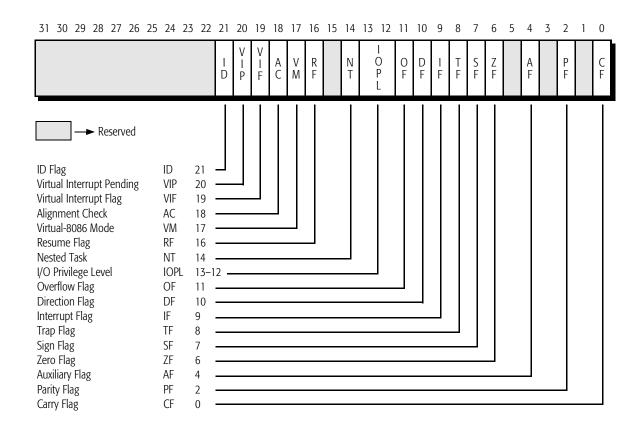

| FIGURE 3- |     | EFLAGS Register                               |       |

| FIGURE 3  |     | Task State Segment (TSS)                      |       |

| FIGURE 3- |     | Machine-Check Address Register (MCAR)         |       |

| FIGURE 3- |     | Machine-Check Type Register (MCTR)            |       |

| FIGURE 5  |     | Signal Groups.                                |       |

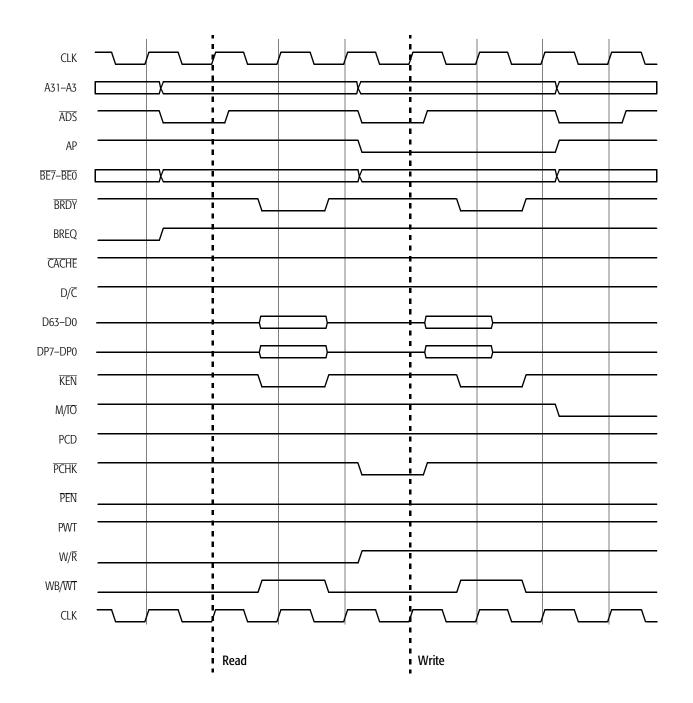

| FIGURE 5  |     | Single-Transfer Memory Read and Write         |       |

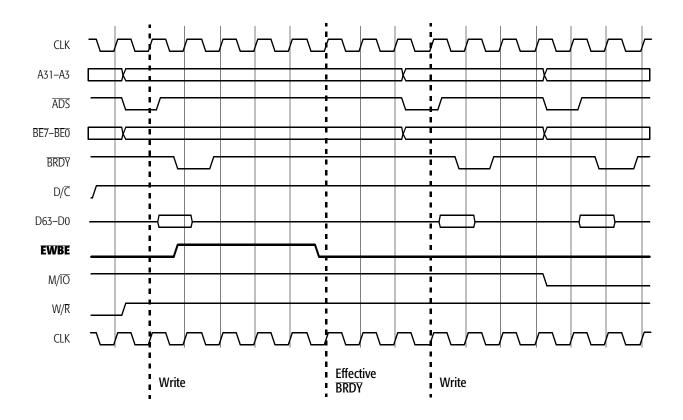

| FIGURE 5  |     | Single-Transfer Memory Write Delayed by       |       |

|           |     | EWBE Signal                                   | 5-146 |

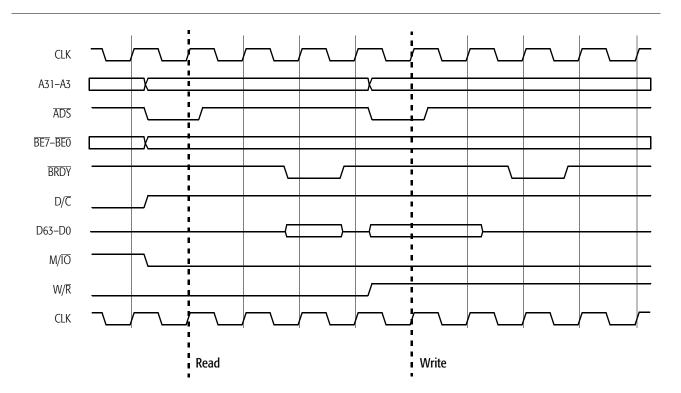

| FIGURE 5  |     | I/O Read and Write                            |       |

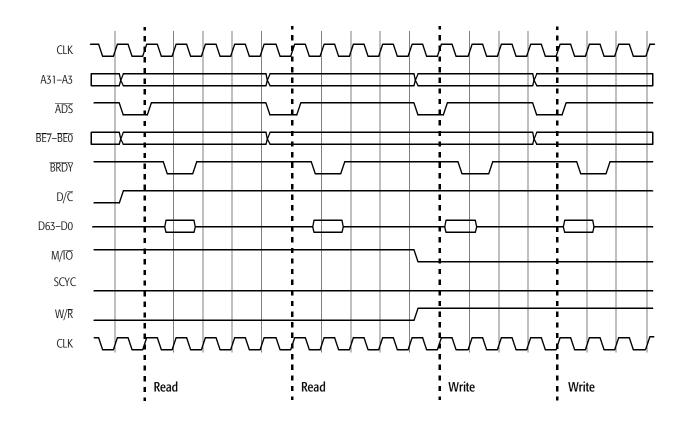

| FIGURE 5  | -5. | Single-Transfer Misaligned Memory and         |       |

|           |     | I/O Transfers                                 | 5-149 |

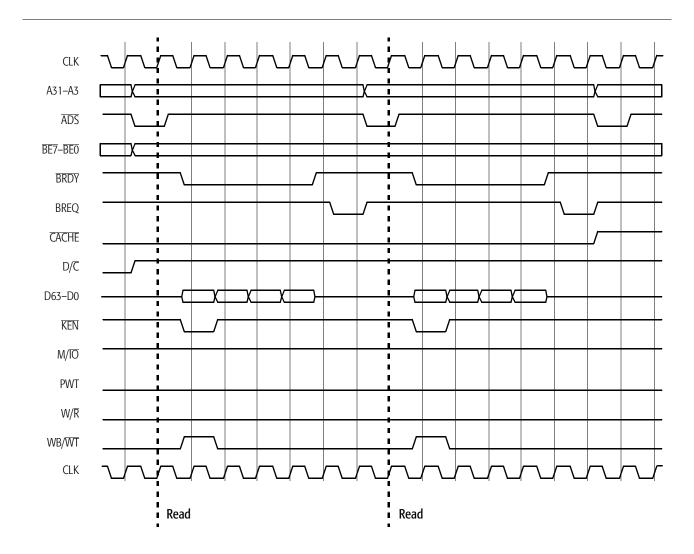

| FIGURE 5  | -6. | Burst Reads                                   | 5-152 |

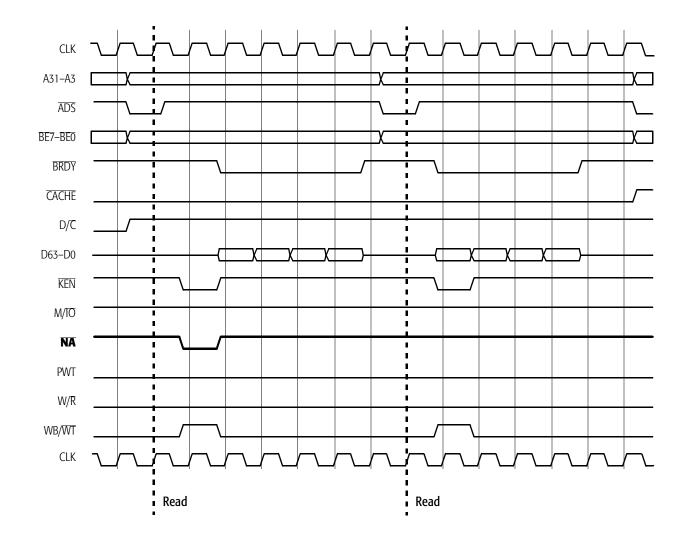

| FIGURE 5  |     | Burst Read (NA Sampled)                       |       |

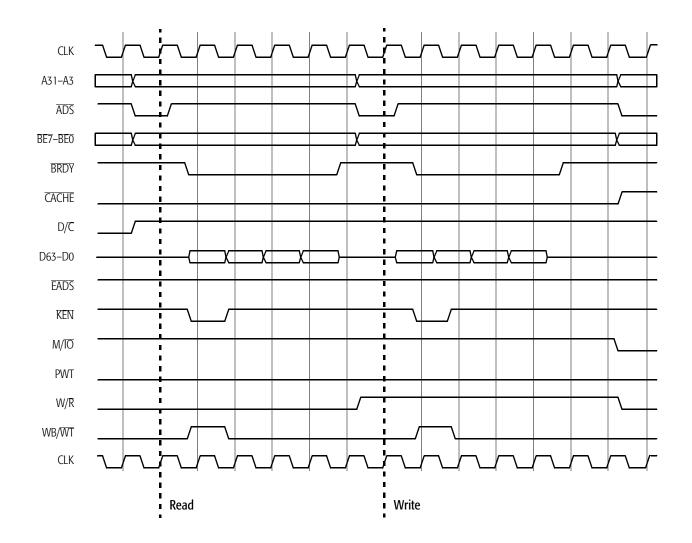

| FIGURE 5  |     | Burst Writeback Due To Cache-Line Replacement |       |

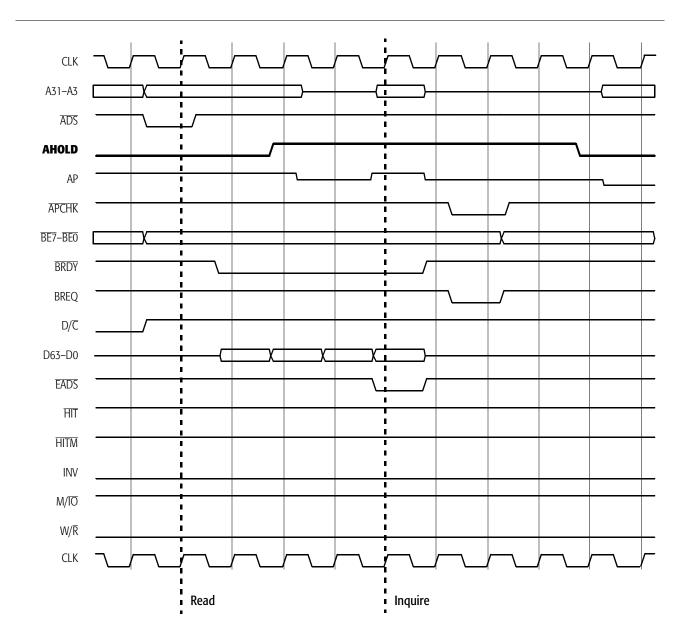

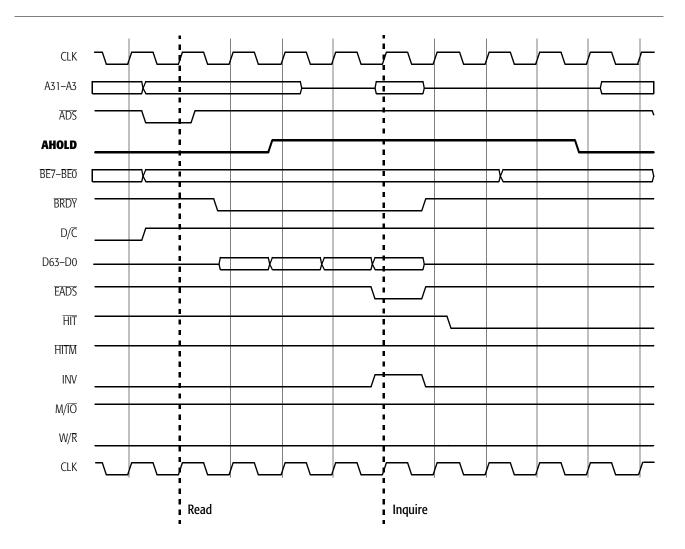

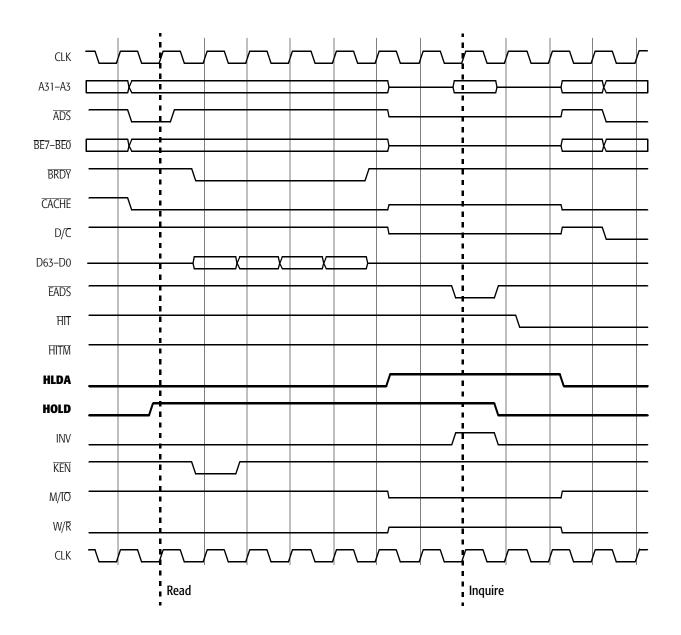

| FIGURE 5  |     | AHOLD-Initiated Inquire Miss                  |       |

| FIGURE 5  |     | AHOLD-Initiated Inquire Hit to Shared or      |       |

|           |     | Exclusive Line                                | 5-160 |

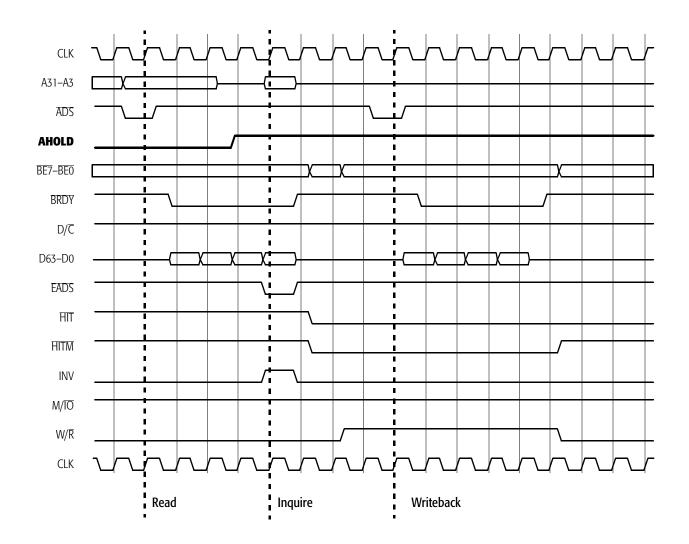

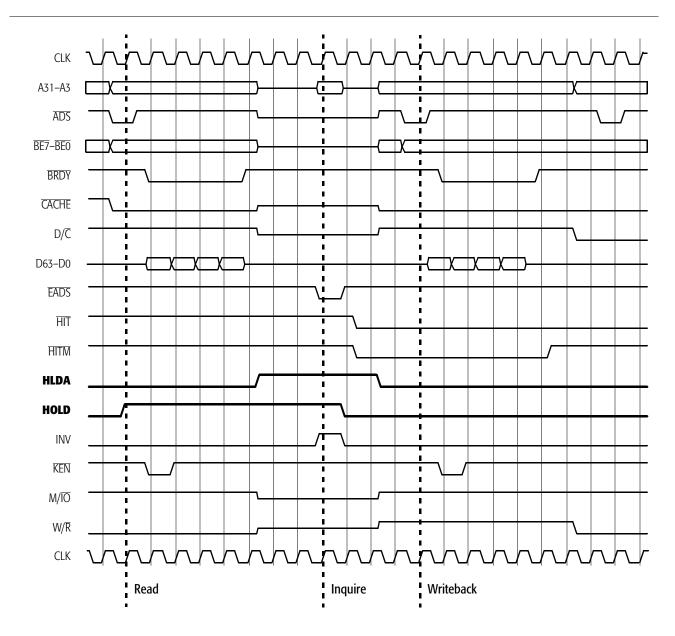

| FIGURE 5  |     | AHOLD-Initiated Inquire Hit to Modified Line  |       |

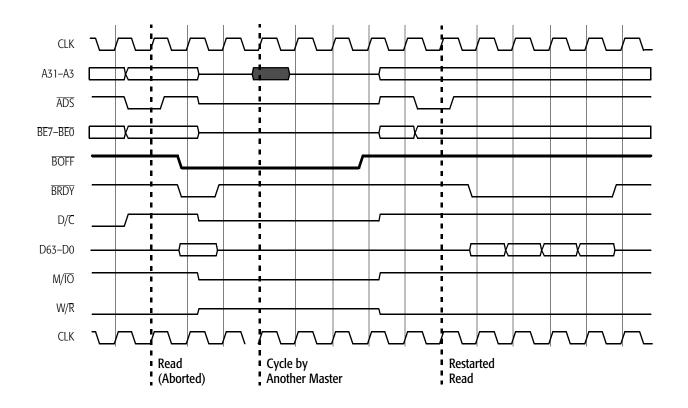

| FIGURE 5- |     | Basic BOFF Operation                          |       |

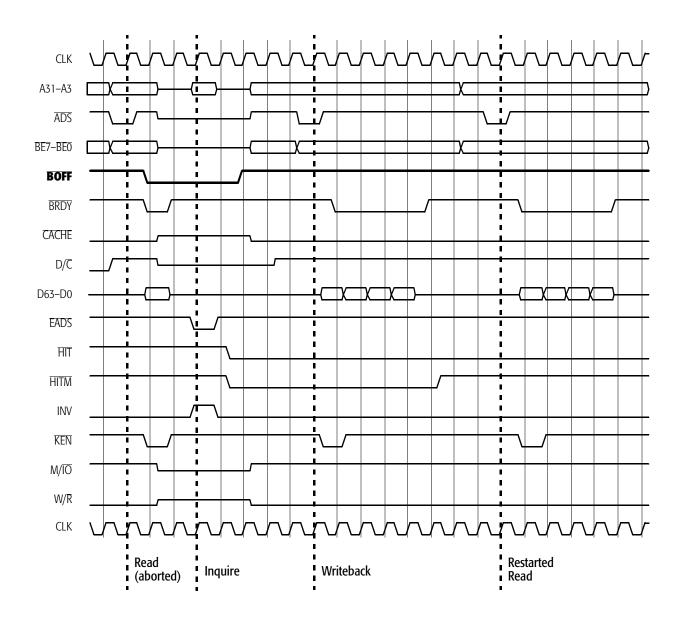

| FIGURE 5- |     | BOFF-Initiated Inquire Hit to Modified Line   |       |

| FIGURE 5  |     | HOLD-Initiated Inquire Hit to Shared or       |       |

|           |     | Exclusive Line                                | 5-168 |

| FIGURE 5  |     | HOLD-Initiated Inquire Hit to Modified Line   |       |

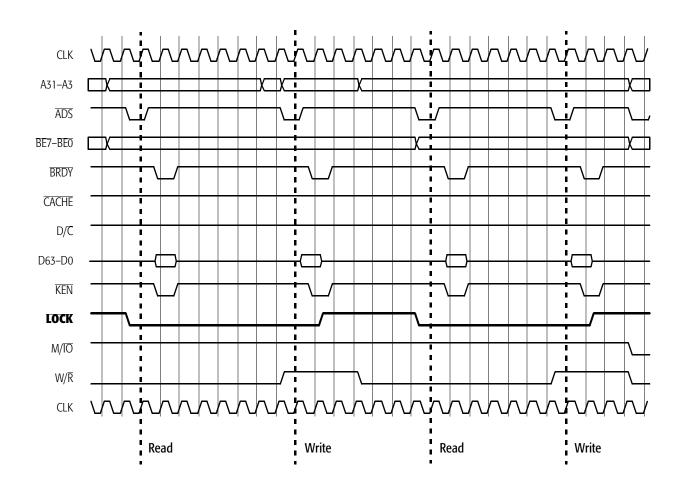

| FIGURE 5  |     | Basic Locked Operation                        |       |

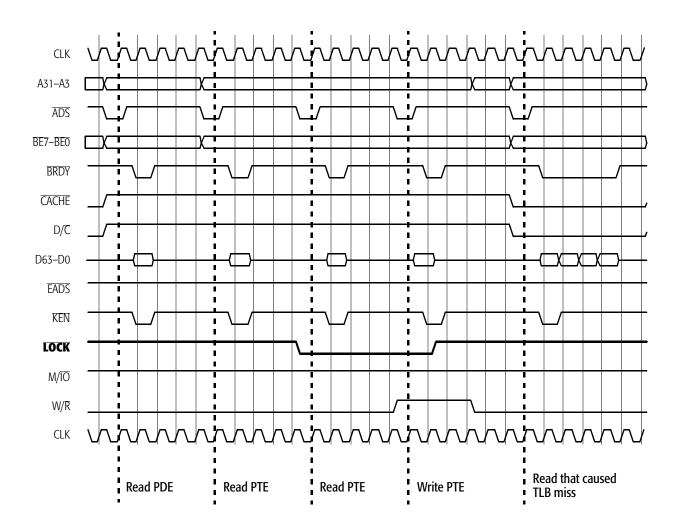

| FIGURE 5  |     | TLB Miss (4-Kbyte Page)                       |       |

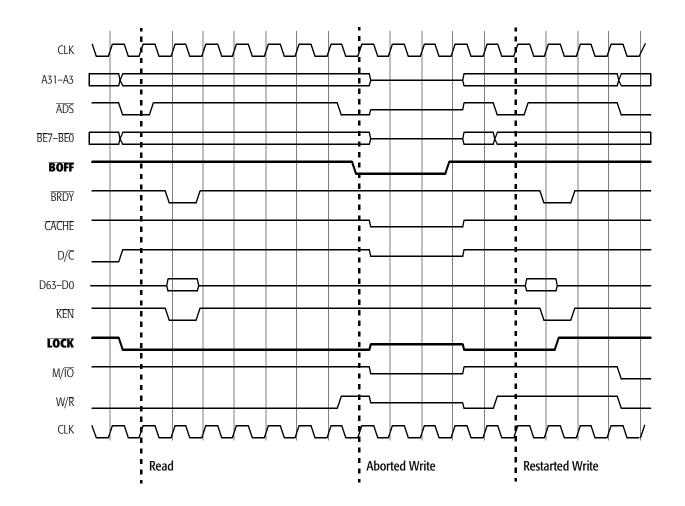

| FIGURE 5  |     | Locked Operation with BOFF Intervention       |       |

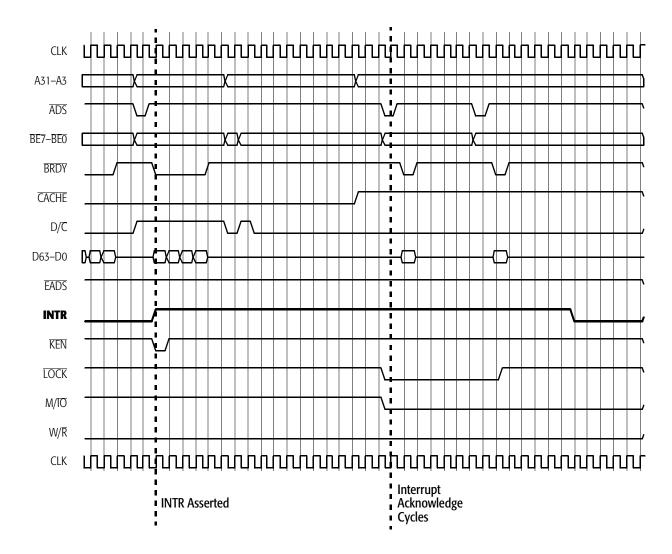

|           |     | Interrupt Acknowledge Operation Part 1        |       |

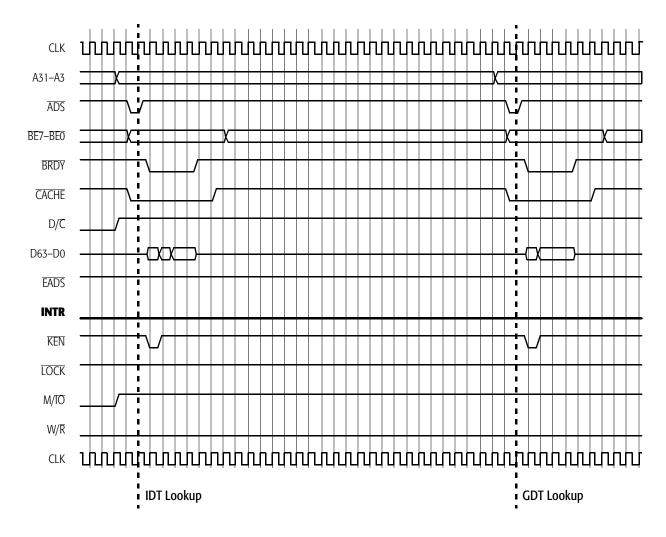

|           |     | Interrupt Acknowledge Operation Part 2        |       |

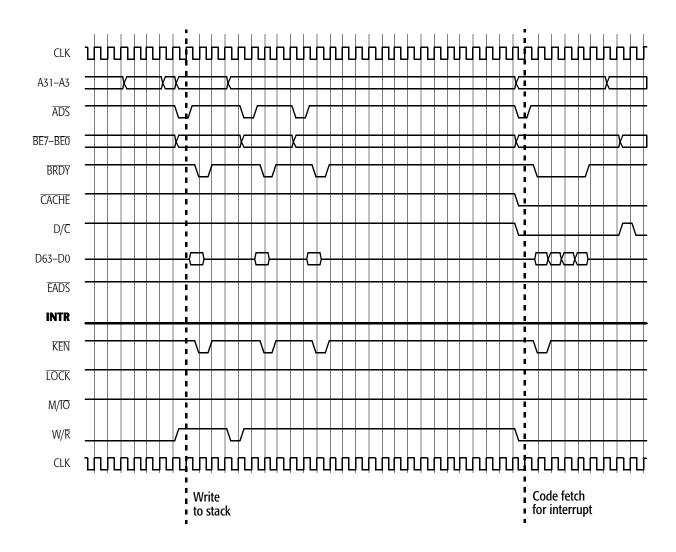

|           |     | Interrupt Acknowledge Operation Part 3        |       |

| FIGURE 5- |     | Basic Special Bus Cycle (Halt Cycle)          |       |

| FIGURE 5  |     | Shutdown Cycle                                |       |

| FIGURE 5  |     | FLUSH-Acknowledge Cycle                       |       |

| FIGURE 5  |     | Cache-Invalidation Cycle (INVD Instruction)   |       |

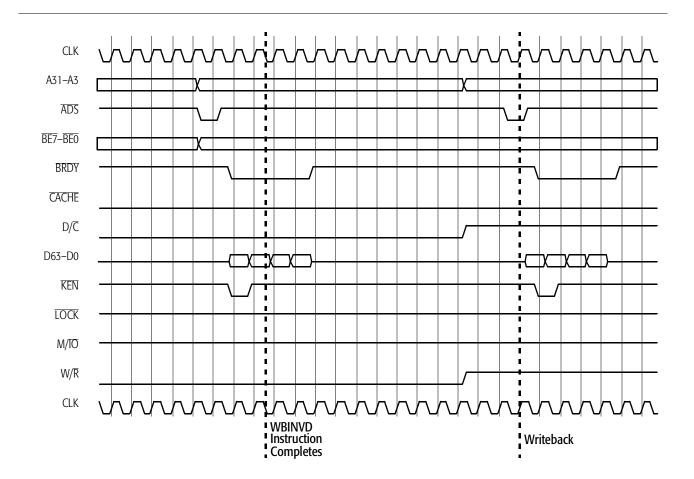

|           |     | Cache-Writeback and Invalidation Cycle        |       |

|           |     | (WBINVD Instruction) Part 1                   | 5-186 |

|           |     | · · · · · · · · · · · · · · · · · · ·         |       |

| FIGURE | 5-24B. | Cache-Writeback and Invalidation Cycle               |

|--------|--------|------------------------------------------------------|

|        |        | (WBINVD Instruction) Part 2 5-187                    |

| FIGURE | 5-25.  | Branch-Trace Message Cycle 5-189                     |

| FIGURE | 5-26A. | Transition from Normal Execution to SMM Part 1 5-191 |

| FIGURE | 5-26B. | Transition from Normal Execution to SMM Part 2 5-192 |

| FIGURE | 5-27A. | Stop-Grant and Stop-Clock Modes Part 1 5-194         |

| FIGURE | 5-27B. | Stop-Grant and Stop-Clock Modes Part 2 5-195         |

| FIGURE | 5-28.  | INIT-Initiated Transition from Protected             |

|        |        | Mode to Real Mode 5-197                              |

| FIGURE | 6-1.   | Typical Desktop-System BIOS Memory Map 6-3           |

| FIGURE | 6-2.   | Default SMM Memory Map 6-7                           |

| FIGURE | 6-3.   | <b>BOFF</b> Example                                  |

| FIGURE | 6-4.   | AHOLD and BOFF Example 6-18                          |

| FIGURE | 6-5.   | Write-Once Protocol 6-21                             |

| FIGURE | 6-6.   | Clock Control State Transitions 6-36                 |

| FIGURE | 6-7.   | V <sub>cc</sub> and CLK 6-40                         |

| FIGURE | 6-8.   | CLK Delay Function 6-41                              |

| FIGURE | 6-9.   | CLK Synthesizer with Output Enable 6-42              |

| FIGURE | 6-10.  | CPUCLK Clamping Circuit 6-42                         |

| FIGURE | 7-1.   | Hardware Configuration Register (HWCR) 7-3           |

| FIGURE | 7-2.   | Array Access Register (AAR)                          |

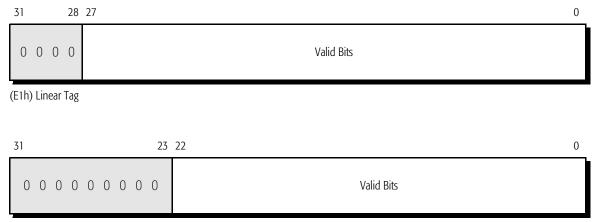

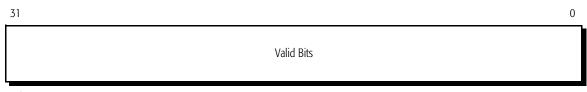

| FIGURE | 7-3.   | Test Formats: Data-Cache Tags 7-10                   |

| FIGURE | 7-4.   | Test Formats: Data-Cache Data 7-11                   |

| FIGURE | 7-5.   | Test Formats: Instruction-Cache Tags 7-12            |

| FIGURE | 7-6.   | Test Formats: Instruction-Cache Instructions 7-13    |

| FIGURE | 7-7.   | Test Formats: 4-Kbyte TLB 7-14                       |

| FIGURE | 7-8.   | Test Formats: 4-Mbyte TLB 7-15                       |

## **List of Tables**

| TABLE 2-1.  | ALU Instruction Classes                                      |

|-------------|--------------------------------------------------------------|

| TABLE 2-2.  | Cache States for Read and Write Accesses 2-19                |

| TABLE 2-3.  | Cache States for Snoops, Invalidation, and Replacements 2-20 |

| TABLE 2-4.  | Snoop Action                                                 |

| TABLE 3-1.  | Control Register 4 (CR4) Fields 3-3                          |

| TABLE 3-2.  | Page-Directory Entry (PDE) Fields 3-8                        |

| TABLE 3-3.  | Page-Table Entry (PTE) Fields 3-11                           |

| TABLE 3-4.  | Virtual-Interrupt Additions to EFLAGS Register 3-15          |

| TABLE 3-5.  | Instructions that Modify the IF or VIF Flags 3-16            |

| TABLE 3-6.  | Interrupt Behavior and Interrupt-Table Access                |

| TABLE 3-7.  | Machine-Check Type Register (MCTR) Fields 3-27               |

| TABLE 4-1.  | Integer Instructions                                         |

| TABLE 4-2.  | Integer Dot Product Internal Operations Timing 4-18          |

| TABLE 4-3.  | Floating-Point Instructions                                  |

| TABLE 5-1.  | Summary of Signal Characteristics 5-4                        |

| TABLE 5-2.  | Conditions for Driving and Sampling Signals 5-9              |

| TABLE 5-3.  | Summary of Interrupts and Exceptions 5-17                    |

| TABLE 5-4.  | Address-Generation Sequence During Bursts 5-22               |

| TABLE 5-5.  | Relation Of BE7-BE0 To Other Signals 5-35                    |

| TABLE 5-6.  | Encodings For Special Bus Cycles                             |

| TABLE 5-7.  | Processor-to-Bus Clock Ratios 5-37                           |

| TABLE 5-8.  | Outputs Floated When BOFF is Asserted 5-39                   |

| TABLE 5-9.  | MESI-State Transitions for Reads                             |

| TABLE 5-10. | Relation Between D63–D0, BE7–BE0, and DP7–DP0 5-57           |

| TABLE 5-11. | MESI-State Transitions for Inquire Cycles 5-73               |

| TABLE 5-12. | Outputs Floated When HLDA is Asserted 5-76                   |

|             | Interrupt Acknowledge Operation Definition 5-86              |

| TABLE 5-14. | PWT, Writeback/Writethrough, and MESI 5-106                  |

| TABLE 5-15. | Register State After RESET or INIT 5-111                     |

|             | Outputs at RESET 5-113                                       |

| TABLE 5-17. | MESI-State Transitions for Reads 5-135                       |

| TABLE 5-18. | MESI-State Transitions for Writes 5-136                      |

| TABLE 5-19. | Bus Cycle Definitions 5-137                                  |

| TABLE 5-20. | Bus-Cycle Order During Misaligned Transfers 5-148            |

| TABLE 5-21. | Address-Generation Sequence During Bursts 5-151              |

|             | Interrupt Acknowledge Operation Definition 5-176             |

| TABLE 5-23. | Encodings For Special Bus Cycles 5-181                       |

|             | Branch-Trace Message Special Bus Cycle Fields 5-188          |

| TABLE 6-1.  | Initial State of Registers in SMM                            |

| TABLE 6-2.  | SMM State-Save Area Map 6-26                                 |

| TABLE 7-1.  | Hardware Configuration Register (HWCR) Fields 7-4            |

| TABLE 7-2.  | BIST Error Bit Definition in EAX Register                    |

| TABLE 7-3.  | Array IDs in Array Pointers                                  |

|             | -                                                            |

| TABLE 7-4.         | Branch-Trace Message Special Bus Cycle Fields | 7-18 |

|--------------------|-----------------------------------------------|------|

| <b>TABLE 7-5</b> . | Test Access Port (TAP) ID Code                | 7-21 |

| TABLE 7-6.         | Public TAP Instructions                       | 7-22 |

## Preface

This manual describes the technical features of the  $AMD5_K86^{TM}$  processor, and its differences from the Pentium processor, at a level of detail suitable for a hardware designer or system-software developer to implement system boards, core system logic, and system software. Specifically, the manual describes the following aspects of the processor

- Internal architecture

- Software differences from the 486 and Pentium processors

- Performance parameters

- Bus signals functions

- Bus cycle timing

- Design issues for system-board designs

- Test and debugging features

A full description of the x86 programming environment is beyond the scope of this manual. Instead, the software sections describe differences from the 486 processor's programming environment. A list of commercial books that describe the x86 programming environment and other subjects of potential interest appears at the end of this preface.

In addition to descriptions of the  $AMD5_K 86$  processor's unique internal architecture, the manual incorporates details about the behavior of bus signals and bus cycles that are standard to the x86 processors but that are not fully documented in other x86 manuals.

## Notation

The following notation is used in this manual:

*b*—Binary

d—Decimal

h—Hexadecimal

Set—Written with a value of 1

Clear—Written with a value of 0

GP(0)—General-protection exception (13 decimal) with an error value of 0

EFLAGS.IF—The IF bit in the EFLAGS register

CS:EIP—A logical address, expressed as a segment selector (CS) and offset (EIP)

000F\_FFF0h—A physical-memory address using hexadecimal notation

## Terminology

The following definitions apply throughout this document:

- Pin and Signal—A pin is a piece of metal on the processor's package. A signal is the information about logical states that a pin carries. Pins have pin numbers; signals have signal names. On processors that multiplex signals, pins can carry more than one signal; the AMD5<sub>K</sub>86 processor, however, does not multiplex signals in this manner.

- Assert and Negate—A signal that is driven or sampled active is asserted. A signal that is inactive is negated. In general, asserted means sampled asserted either by the processor or target logic. Signals that are active in a Low-voltage state, such as BRDY, are shown with an overbar. Signals that are active in a High-voltage state, such as INTR, are shown without an overbar. Dual-state signals, such as R/S and WB/WT, have two states of assertion and, therefore, the term asserted has no meaning; such dual-state signals are driven High or Low.

- Drive and Sample—A single-state signal is driven when it is asserted or negated by a logic device; it is sampled when its driven state is detected by another device.

- *Cycle and Clock*—This term commonly refers to at least four different things:

- *Bus-clock period:* The cycle time of the CLK signal.

- *Processor-clock period:* The cycle time of the processor's internal clock, which has a frequency relative to CLK that is determined by the state of the BF signal during RESET. Whenever this cycle is meant, such as in the Chapter 4 description of pipeline timing and the instruction latency, the full name, *processor-clock cycle*, is used.

- *Bus cycle:* A signal protocol on the processor's bus, such as a single-transfer read cycle or a special bus cycle.

- *Sequence of bus cycles:* One or more contiguous bus cycles. For example, the two bus cycles that constitute an interrupt acknowledgment are called a bus *operation*, so that the constituent bus cycles can be distinguished from the entire operation.

- *Writeback*—This term refers to two related concepts:

- *Bus Cycle*—A 32-byte burst write cycle to a memory block that has been cached in the *modified* state. Writebacks can be caused by inquire cycles, internal snoops, writeback and invalidate operations (such as FLUSH or the WBINVD instruction), cache-line replacements, or locked operations on cached locations. It is sometimes called a *copyback*.

- *Cache-Line State*—A cache line in the *modified* or *exclusive* MESI state (modified, exclusive, shared, invalid).

- *Writethrough*—This term refers to two related concepts:

- *Bus Cycle*—A 1-to-8-byte, single-transfer write cycle caused by write misses or write hits to lines in the *shared* or *exclusive* MESI state.

- Cache-Line State—A cache line in the shared MESI state.

- *Flush*—This term commonly refers to at least four things and is usually avoided in favor of the following specific terms:

- *Pipeline Invalidation:* A pipeline-flush operation invalidates instructions in the pipeline that have not been retired (and, depending on the type of pipeline invalidation, entries in the reorder buffer, entries in the TLB, and/or branch-prediction bits) without writing their state to any storage resource.

- *Cache Invalidation:* The INVD instruction invalidates the contents of the instruction and data caches, without writing modified data back to memory.

- *Cache Writeback and Invalidation:* The WBINVD instruction writes *modified* lines in the data cache back to memory while invalidating each line in the instruction and data caches.

- *FLUSH Operation:* The FLUSH input signal executes the same microcode routine as the WBINVD instruction to write *modified* lines in the data cache back to memory while invalidating each line in the instruction and data caches.

- Flush Acknowledge Cycle—This term commonly refers to different types of special bus cycles driven by the processor, and is therefore avoided in favor of the following specific terms:

- *FLUSH Acknowledge:* A special bus cycle driven after the FLUSH operation completes.

- *INVD Acknowledge:* A special bus cycle driven after the INVD cache invalidation completes.

- *WBINVD Acknowledge:* A sequence of two special bus cycles driven after the WBINVD cache writeback and invalidation completes.

- *Snoop*—This term commonly refers to at least three different actions and is therefore avoided in favor of the following specific terms:

- *Inquire Cycles:* These are bus cycles driven by system logic. They cause the processor to compare the inquire-cycle address with the processor's physical

cache tags. The  $AMD5_{K}86$  and Pentium processors both support inquire cycles.

- *Internal Snooping:* These snoops are initiated by the processor (rather than system logic) during certain types of cache accesses. Both the  $AMD5_K86$  and Pentium microprocessors support this type of internal snooping for the purpose of detecting self-modifying code. See page 2-22 for details.

- Bus Watch: Some caching devices watch their address and data bus continuously while they are held off the bus. They compare every address driven by another bus master with their internal cache tags, and they may also be able to update their cached lines during writebacks to memory by another bus master. Neither the AMD5<sub>K</sub>86 nor Pentium microprocessors support bus watching.

- Cold and Warm Reset—The terms cold or hard reset and warm or soft reset are commonly used to mean three related but different things, and the terms are therefore avoided. A cold or hard reset typically refers to the assertion of RESET at power-up, but warm or soft reset can refer either to the assertion of RESET after power-up or to the assertion of INIT.

- System Logic—Any logic outside the processor, including a core-logic chipset, another bus master, or separate controllers for L2 cache, memory, interrupts, DMA, communications, video, bus bridging, bus arbitration, or any other system function.

## References

- Abel, Peter. *IBM PC Assembly Language and Programming*. Englewood Cliffs: Prentice Hall, 1995.

- Abramovici, Miron; Melvin A. Breuer; and Arthur D. Friedman. *Digital Systems Testing and Testable Design*. New York: IEEE Press, 1990.

- Agarwal, Rakesh. 80x86 Architecture & Programming. Vols. I and II. Englewood Cliffs: Prentice-Hall, 1991.

- Alexandridis, Nikitas. *Design of Microprocessor-Based Systems*. Englewood Cliffs: Prentice-Hall, 1993.

- Anderson, Don, and Tom Shanley. *Pentium Processor System Architecture*. Reading: Addison-Wesley, 1995.

- Barkakati, Nabajyoti, and Randall Hyde. *Microsoft Macro Assembler Bible*. Carmel: Sams, 1992.

- Brey, Barry B. The Intel 32-Bit Microprocessors. Englewood Cliffs: Prentice Hall, 1995.

- Brown, Ralf, and Jim Kyle. *PC Interrupts, A Programmer's Reference to BIOS, DOS, and Third-Party Calls*. Reading: Addison-Wesley, 1994. For an updated version on the Internet, ftp to oak.oakland.edu and get file /pub/msdos/info/inter41.zip.

- Brumm, Penn, and Don Brumm. 80386/80486 Assembly Language Programming. Windcrest: McGraw-Hill, 1993.

- Chappell, Geoff. DOS Internals. Reading: Addison-Wesley, 1994.

- Crawford, John H., and Patrick P. Gelsinger. *Programming the* 80386. San Francisco: Sybex, 1987.

- Giles, William B. Assembly Language Programming for the Intel 80xxx Family. New York: Macmillan, 1991.

- Handy, Jim. The Cache Memory Book. San Diego: Academic Press, 1993.

- Hennessy, John L., and David A. Patterson. *Computer Architecture, A Quantitative Approach.* 2d Ed. San Francisco: Morgan Kaufmann Publishers, 1996.

- Hogan, Thom. The Programmer's PC Sourcebook. Redmond: Microsoft Press, 1991.

- Hwang, Kai. Advanced Computer Architecture. New York: McGraw-Hill, 1993.

- Institute of Electrical and Electronics Engineers. *IEEE Standard for Binary Floating-Point Arithmetic.* ANSI/IEEE Std 754-1985.

- Institute of Electrical and Electronics Engineers. *IEEE Standard for Radix-Independent Floating-Point Arithmetic*. ANSI/IEEE Std 854-1987.

- Institute of Electrical and Electronics Engineers. *IEEE Standard Glossary of Mathematics of Computing Terminology*. ANSI/IEEE Std 1084-1986. Out of print.

- Johnson, Mike. Superscalar Microprocessor Design. Englewood Cliffs: Prentice-Hall, 1991.

- Katz, Randy H. Contemporary Logic Design. Redwood City: Benjamin Cummings, 1994.

- Morse, Stephen P.; Eric J. Isaacson; and Douglas J. Albert. *The 80386/387 Architecture*. New York: John Wiley & Sons, 1987.

- Norton, Peter; Peter Aitken; and Richard Wilton. *PC Programmer's Bible*. Redmond: Microsoft Press, 1993.

- Parker, Kenneth P. The Boundary-Scan Handbook. Boston: Kluiver, 1992.

- Patterson, David A., and John L. Hennessy. *Computer Organization and Design: The Hardware/Software Interface*. San Francisco: Morgan Kaufmann Publishers, 1994.

- Phoenix Technical Reference Series. System BIOS for IBM PCs, Compatibles, and EISA Computers. Reading: Addison-Wesley, 1991.

Pietrek, Matt. Windows Internals. Reading: Addison Wesley, 1993.

- Richter, Jeffrey. Advanced Windows NT. Redmond: Microsoft Press, 1994.

- Ro, Sen-Cuo, and Sheau-Chuen Her. *i386/i486 Advanced Programming*. New York: Van Nostrand Reinhold, 1993.

- Slater, Michael. Microprocessor-Based Design. Englewood Cliffs: Prentice-Hall, 1989.

- Stallings, William. Operating Systems. New York: Macmillan, 1992.

- Van Gilluwe, Frank. The Undocumented PC. Reading: Addison-Wesley, 1994.

- Wakerly, John F. Digital Design Principles and Practices. Englewood Cliffs: Prentice-Hall, 1994.

- Wharton, John. The Complete x86. Sebastopol, CA: MicroDesign Resources, 1994.

# 1

## **Overview**

The AMD5<sub>K</sub>86<sup>TM</sup> processor brings superscalar RISC performance to desktop systems running industry-standard x86 software. The processor implements advanced design techniques like instruction pre-decoding, single-cycle internal RISC operations, parallel execution units, out-of-order issue and completion, register renaming, data forwarding, and dynamic branch prediction. The processor's many test and debug features support fast, reliable designs for x86 desktop systems.

AMD's development and support of the popular Am386<sup>®</sup> and Am486<sup>®</sup> processors has given it a broad foundation of experience in the x86 architecture. The AMD5<sub>K</sub>86 processor's binary compatibility with DOS and Windows<sup>®</sup>-compatible software running on the Pentium processor and all previous x86 processors has been established in extensive testing, using industry-standard test tools. Compatibility and qualification testing has also been provided by leading desktop-system manufacturers, chip-set manufacturers, and the independent XXCAL testing laboratory.

The result can be seen in the  $AMD5_{K}86$  processor's performance. This performance plus its compatibility with an immense library of existing x86 software make the  $AMD5_{K}86$  processor a leading-edge solution for desktop systems.

## **1.1** Features

- Pentium-Processor Standard

- Compatible with the Pentium (735\90, 815\100) processor 296-pin socket

- Compatible with existing Pentium (735\90, 815\100) processor support infrastructure and system designs

- Compatible with Pentium, 486, and 386 processor software

- Compatible with x86 DOS, Microsoft<sup>®</sup> Windows<sup>®</sup> operating system, and the large installed base of x86 software

- Compatible with IEEE 854 floating-point standard

- Selectable bus frequencies

- Support for multiprocessing

- High-Performance Execution

- Six execution units (two ALUs, two load/store, one branch, one floating-point)

- Up to four instructions issued per processor clock

- Out-of-order issue and completion

- Speculative execution along three predicted branches

- Register renaming

- Data forwarding

- Predecoder converts x86 instructions to single-cycle RISC operations (ROPs)

- Fast integer multiply (4-cycle, fully pipelined)

- Five-stage pipeline

- Single-cycle cache access

- Zero-delay branching, 3-clock misprediction penalty (often hidden)

- No mixed-operand-size penalty

- No prefix penalty

- Single-cycle misalignment penalty

- No instruction-pairing requirements for parallel issue

- No pipeline invalidation on segment loads

- Efficient support for 16- and 32-bit code, with mixed operand sizes

- High-Performance Cache and TLBs

- 16-Kbyte instruction cache supports split-line access