# Executive letter CULIVE IELET

(above L-R) Dave Saathoff, Chief Administrative Officer Mark Melliar-Smith, President and Chief Executive Officer Rinn Cleavelin, Chief Operating Officer 2000 was a year of celebration. With the full membership of Hyundai, Infineon, Philips, STMicroelectronics, and TSMC, we became one global consortium, made up of thirteen companies representing Asia, Europe, and the United States, dedicated to cooperative efforts to improve semiconductor manufacturing technology. More than ever, our diversity is our strength. Unified by a common mission and governed by consensus, International SEMATECH (ISMT) represents a unique and rich blend of corporate and regional cultures. New perspectives, ideas, and approaches continue to broaden our capabilities, refine our processes, and generate successful results for our members.

2000 was a year of renewed commitment, as "Realize the Roadmap" became our prime directive. During the strategic planning process our Board of Directors and Executive Steering Council defined International SEMATECH's mandate to realize the Roadmap in six key focus areas: post-193 nm lithography, 193 nm optical extension, mask cost and availability, low-k materials, future gate stack, and manufacturing effectiveness. Our mission is to focus on critical technical challenges specified in the *International Technology Roadmap for Semiconductors* in these six key areas. We will accomplish this mission by concentrating on those programs best done in a pre-competitive consortium environment, delivering our programs when our members need them to stay on the Roadmap, and cooperating with and leveraging other sources of R&D for the benefit of our members.

We have undertaken the mission enthusiastically. It is not a radical departure from our continuing efforts through the years to help our members stay on the productivity curve defined by Moore's Law. Yet its importance today is even more crucial, as the technology and business challenges facing the industry grow in number, complexity, and urgency, and as the semiconductor industry plays a larger and larger role in fueling the global economy. Our successes in 2000 speak to our commitment to the following:

- Focusing our technology programs on ISMT's core competencies, on what we can do best in each of the six key areas

- Partnering with suppliers, consortia, research institutes, and universities around the world to complement our programs and address industry-wide gaps

- Influencing the direction of the industry and its infrastructure by promoting the free exchange of ideas and best practices, and forging industry consensus

- Playing our part in keeping the semiconductor industry, and the global economy that it drives, strong and vibrant

2000 was a year of achievement. The pages that follow chronicle ISMT's technical program results and highlight the value received by our member companies, the contributions of our assignees, various innovations in our support services, and activities that support our community. We would like to thank our member companies, our advisory boards, our worldwide partners, our local community, and particularly our own employees and assignees for making these achievements possible. We are proud of our efforts, but we are even more proud of the thirteen member companies we serve—for their successes in the marketplace, their commitment to pre-competitive cooperation, and the leadership they exert in the industry and in the world.

Mach Mellier - Smith

Mark Melliar-Smith President and Chief Executive Officer

**Rinn Cleavelin** Chief Operating Officer

**David Saathoff** Chief Administrative Officer

## **Mission**

The members of International SEMATECH will gain manufacturing advantage through cooperative work on semiconductor manufacturing technology.

### Vision

International SEMATECH is the most effective, global consortium influencing semiconductor industry directions and member company capability.

## Values

Customer Focus Technical Excellence Quality Results Accountability Integrity Open Communication Safety Teamwork

## Technology Roundtable: a Conversation with ISMT Technologists

With the increasing demand for portable electronic devices, and the continual push of Moore's law to quadruple the number of transistors on a chip every three years, CMOS scaling is being severely challenged in the drive to the 30 nm technology generation. Several of the leading technologists working at International SEMATECH (ISMT) recently discussed in a roundtable session the limits of—and likely replacement for— CMOS technology.

Peter Zeitzoff, Fellow: Conventional scaling is going to get very tough around the sub-50 nm generation, and certainly beyond that. MOS type devices will likely replace conventional planar CMOS, but they will be somewhat different structures. One of the devices under consideration these days is dual gate SOI or wraparound or vertical gate, which is probably do-able by similar processing techniques and tools that we have today.

Howard Huff, Senior Fellow: It appears that device fabrication down to approximately 15-20 nm channel length may be possible by utilizing the full suite of alternative MOSFET device configurations, which not only includes the vertical gate transistor that Peter referred to, but also the elevated source/drain, drain only, FinFET, ballistic transistor and additional alternative device configurations. Ken Monnig, Associate Director, Interconnect: The Moore's law model has been predicated on planar MOS. It was planar

PMOS for a while, and planar NMOS for a while, and planar CMOS for a while. Through all of that, we've been essentially gaining our performance by shrinking and not really doing too much to the device or to the processes. Now we are getting to the point where we are running into fundamental material limits and, yes, we can move to three dimensional devices to get us one more step on the Moore's law curve. And then we can move to optical interchip communication to get us one more step on the Moore's law curvestep. So each successive step on the Moore's law curve becomes increasingly more difficult, and the main question you have to ask yourself is: Are we ever going to get the return on the investment that you made to make that step? And that is, in some sense, not a technical question.

So, the question is: can we implement those solutions in a timely fashion, at a reasonable cost, and how many more generations on this sort of Moore's law performance versus dollar curve does that implementation buy you? Copper and low-k interlevel dielectric are another one of those things that, when you look at it, if you don't do anything else, if you do conventional scaling, you get one or two more generations out of it.

John Canning, NGL Program Manager: Lithography has been a key technology driver of smaller and faster devices. Extensions of optical lithography—by shorter wavelengths, higher numerical apertures, off-axis illumination, improved resist processes, and phase shifting masks—have driven the Roadmap on a two-year cycle down to the 100 nm node and possibly to 70 nm. Next Generation Lithography, such as EUV and EPL, holds the promise to go to 25 nm. A major concern is the economics: Will the cost-of-ownership be affordable, and can the mask industry fund the required R&D?

Another concern is the availability of interconnect materials with a resistivity lower than copper.

Monnig: If you continue to do conventional scaling, the Roadmap tells you to stay on the current performance curves, then yes, you would have to come up with another material by the 70 nm node, maybe 35 nm. Canning: By what node?

Monnig: It depends on how far you think you can really push the dielectric constant, because there are really two materials at play here. There aren't any other materials in the periodic table that are lower resistivity than copper, except silver, and it's only about 10 percent less. It's not a technology generation's worth of less. So then what do you do? You could cool the devices, but that's a really big step. And when you look at that, you can squeeze maybe another generation or two out of it. Zeitzoff: With the interconnect, you really hit the material limits that Ken mentioned very fast. But, in fact, the performance of ICs has

(below L-R) Alain Diebold, Senior Fellow John Canning, NGL Program Manager Ken Monnig, Associate Director, Interconnect

## Roundtable (continued)

continued to improve rapidly because circuit designers have utilized clever and innovative circuit and architectural techniques to move around some of these apparent limits.

Huff: A system-level approach may indeed offer significant insight into those materials and process changes that will ultimately affect the device performance as observed at the consumer level.

Alain Diebold, Senior Fellow: In addition to worrying about the resistivity of copper lines when they get really thin, we are also concerned that more and more of the devices you want to make are for lower power than laptops—handhelds. You want the battery in your camera to last forever. Right now many of the things in the handhelds aren't quite at the technology edge, but they'll get there sooner and sooner as you want your telephone to be your PC.

Many other proposed technical advances will change our future. The lightweight, plastic display that can show a newspaper or a book, and then be folded and put in your pocket is one that fascinates me. We would have to have thin film transistors and liquid crystal or whatever kind of display technology built into it. You could imagine reading the newspaper one minute and be talking on the telephone to your kids the next minute with this device. All of those things drive totally different kinds of chips than we have considered in the past. Zeitzoff: Your MOSFET device problems get complicated very quickly by going to very low power. You can tolerate pretty thin oxide-based gate dielectrics- (down to almost 1.0 nm) —where the total device leakage limits are relatively high, and hence, the gate leakage can be relatively high. But when you go to a very low power application where the total device leakage must be very low, then the gate leakage must also be quite low. To achieve such a low gate leakage requires a thicker (typically > 1.5 nm) gate oxide, but this thicker oxide usually results in poorer MOSFET device performance. To both control the gate leakage and to get high device performance, a high-k gate dielectric can be used. Timely availability

of production-worthy high-k gate technology is being actively pursued.

Huff: In addition to more power-tolerant chip architecture IC designs, we might also apply more sophisticated power management schemes.

Walter Worth, Fellow: Another challenge that comes along with the shrinking of design rules is the accelerating pace of introduction of low-k interlevel dielectrics and the active developmental work in high-k gate dielectrics. There are new metal-based oxides, organic and siloxane compounds, as well as a variety of exotic CVD precursors. It becomes a real challenge for the industry to receive the necessary ESH data for these materials in step with the timeline for development of the new processes and tools, and their introduction into manufacturing. These ESH data are essential to identify any potential hazards early enough to switch to alternatives or to design in cost-effective administrative and equipment controls to protect the factory personnel and the environment.

Huff: Another important discussion that has been taking place in conjunction with the International Technology Roadmap for Semiconductors [ITRS] involves 450 mm wafers. As we are now entering the 300 mm wafer era, we are already hearing indications that 450 mm wafers may be necessary. Today, 450 mm is but a metaphor for a major productivity enhancement required by the industry to stay on our present business and economic growth trend. An actual wafer diameter change to 450 mm, however, will be needed if no other new productivity improvements are available, and these wafer size changes are always fraught with both economic and technical issues. Continuing to maintain a two-year technology cycle, as tactically envisioned in the ITRS, provides partial mitigation of the need for the next wafer size change, potentially delaying it on nearly a year-by-year basis. Assessment of these highlevel ITRS strategies should be possible using the industry economic and productivity models presently under development at ISMT.

(below L-R) Howard Huff, Senior Fellow Walter Worth, Fellow Peter Zeitzoff, Senior Fellow

# Providing Resources and Direction

(above L-R) Linda Wilson, ITRS Information Manager Sarah Mangum, ITRS Webmaster

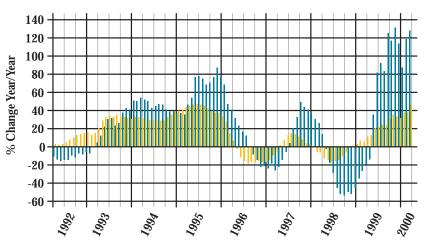

Before SEMATECH began operations, chip manufacturers, equipment and materials suppliers, national research labs, and university researchers gathered to set the charter for the new consortium. Known as roadmapping working groups, these teams created the blueprint for the consortium that would eventually become recognized as world class. The roadmapping that defined SEMATECH's operating plan resulted in another collective effort that would ultimately set the path for the entire semiconductor industry: a commitment to publish the first U.S. national semiconductor industry Roadmap in 1992. SEMATECH provided key technical support for this national task force. roadmap and served as publisher of the document. Eight years later, International SEMATECH (ISMT) remains a key partner in this very important worldwide effort, known as the International Technology Roadmap for

Semiconductors or ITRS. ISMT is involved in the ITRS at every stage of the roadmapping effort. The chair of the ITRS, Paolo Gargini of Intel, is a member of ISMT's Executive Steering Council (ESC), as is Fred Roosmalen of Philips, one of the European representatives on the International Roadmap Committee (IRC). Moreover, six of the twelve ITRS Working Group co-chairs in 2000 represented ISMT's efforts in Lithography, Metrology, Defect Reduction, Process Integration, Front End Processes, and Interconnect. In addition to those six Working Groups, ISMT technical experts actively participate in several other International Technology Working Groups (ITWGs). Representatives from ISMT's Interconnect, Front End Processes, Lithography, and Manufacturing Methods and Productivity divisions were also directly involved in the review or update of the overall Roadmap technology characteristics data for 2000 as part of the Chip Size Study Group task force.

During 2000, International SEMATECH's ITRS department coordinated several activities for the 2000 ITRS Update including continued management of the ITRS website, consulting and management of the April ITWG/IRC meeting hosted by the European IRC members in Leuven, Belgium at IMEC, hosting the annual ITRS summer conference in San Francisco, and consulting and support for the Taiwan-hosted ITRS conference in HsinChu, Taiwan.

ISMT published updated tables from each Working Group for the 2000 ITRS Update,

coordinated all international communications among Working Groups, and posted all conference information and drafts to the ITRS website. The result of the year-long effort: on-time worldwide delivery of the on-line 2000 ITRS Update.

International SEMATECH's hands-on involvement in the ITRS gives member companies a preview of the 15-year assessment of industry technology, helping them to stay on the productivity curve. Through active participation in the ITRS Working Groups, ISMT member companies help define the potential solutions to key challenges, such as gate stack materials, mask cost, novel device structures and metrology at sub-70 nm. Member companies also gain exposure to manufacturers, suppliers, consortia, and academics from around the world. These relationships help foster the informal learning and exchange of pre-competitive technical expertise that helps our members realize the technological Roadmap.

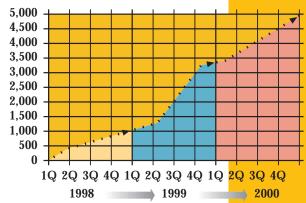

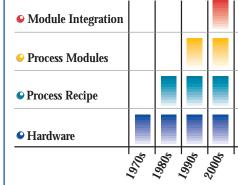

#### (below)

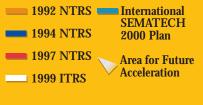

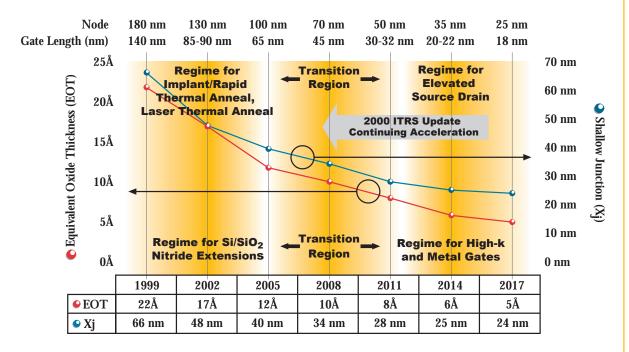

ISMT implementation of the Roadmap with acceleration for members and suppliers beginning in 2003 as shown in the shaded portion.

## Semiconductor Roadmap Acceleration

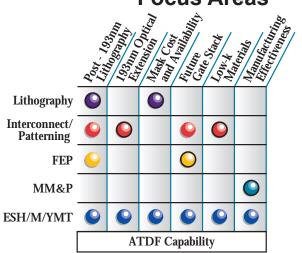

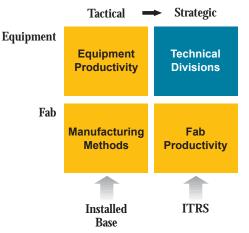

## Realizing the Roadmap in Six Key Focus Areas

In the spring, the Board of Directors' Strategic Planning Subcommittee made a simple pronouncement on International SEMATECH's (ISMT's) strategic role over the next five years—"International SEMATECH," it said, "should help its members realize the Roadmap." The International Technology Roadmap for Semiconductors (ITRS) is a momentous plan for the industry to make itself 1,000 more times productive in fifteen years than it is today, and it is fraught with myriad technical challenges that must be overcome if the industry is to succeed. ISMT's role is to tackle those challenges, and to ensure that the materials, tools, and technology needed by the member companies to stay on the ITRS, or on

## **Focus Areas**

#### (above)

International SEMATECH launched a concerted effort to focus resources on six key areas of wafer fabrication. Division champions were identified, and enabling areas provided needed support.

their own internal roadmaps, will be available when they need them. According to OB Bilous, the consortium's new Chairman of the Board who led the strategic planning efforts, "The mission is not new; International SEMATECH has for years been working to keep its members on the historic productivity curve. But it has a new urgency. The industry is facing tremendous technology and business challenges more formidable and more complex than ever before. The prize for those who succeed in staying on the productivity curve will be continued growth and prosperity and failure for those who don't. It is clear to the Board that International SEMATECH must play a pivotal role in keeping the industry on track."

ISM'T's senior technical advisors, the Executive Steering Council (ESC), concurred with the Board's "Realize the Roadmap" mandate, and further advised ISMT to focus its efforts on six critical Roadmap challenges in 2000-2001:

- Post-193 nm lithography

- 193 nm optical extension

- Mask cost and availability

- Future gate stack (with compatible ultra shallow junction)

- Low-k materials (k < 2.5)

• Manufacturing effectiveness In each of these six key focus areas, the member companies affirmed that they look to ISMT to concentrate on programs best done in a consortium dedicated to pre-competitive cooperation—solving industry infrastructure issues, working on early materials efforts to reduce the number of potential options, working with suppliers on tool evaluation and improvement, and providing a single voice to the industry in areas such as economic modeling and standards.

In carrying out year 2000 programs, and particularly in developing annual plans for 2001. International SEMATECH launched a concerted effort to focus its resources on the six key areas. Division champions were identified, programs were designed and approved by the various advisory groups, partnerships were proposed and formed, and detailed 2001 project plans were solidly in place by year-end. Although ISMT remains a functional organization by technical divisions and enabling areas such as metrology/yield management, environment safety and health, and the Advanced Technology Development Facility (ATDF), the consortium has reorganized its efforts to focus on the few, most critical challenges identified by the members.

Focus areas will, of course, change over time; as technology challenges are met and overcome, new sets of challenges will take their place. International SEMATECH remains committed to concentrating programs on the issues most critical to the collective membership, and to delivering program results that "Realize the Roadmap" for its members.

(**above**) **OB Bilous**, Chairman of the Board

## Expanding Global Connections, Forging Innovative Partnerships

The acceleration, increasing complexity, and rising costs of technology development in the industry make it clear that no company, nation, or region can hope to stay on the Roadmap without sharing the risks and rewards of technology research and development with global partners. Boundaries are disappearing, the members are engaging in growing numbers of alliances and joint ventures around the world, and International SEMATECH (ISMT) is nurturing its own network of global connections. To realize the Roadmap, ISMT continues to seek out world-class expertise wherever it resides to complement programs, bridge gaps in knowledge, and minimize duplication of effort.

Global membership and connections make ISMT an excellent catalyst for collaboration. Members look to ISMT to take the initiative in forming and managing partnerships with suppliers, consortia, research institutes, and universities worldwide, and ISMT takes pride in having put together a series of innovative and successful partnerships.

(below L-R)

Ed Strickland.

International

Jackie Ferrell.

Program Manager,

SEMATECH/SRC

Program Manager,

Randy Goodall,

Project Manager,

Water Optimization

Jerry Chen,

**FEP Research Center**

Guidelines and Standards

MM&P Associate Director

External Research and

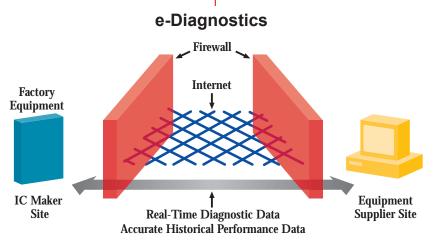

ISMT's Industry Executive Forums (IEF), led by Dave Anderson, director of Supplier Relations, bring together senior executives from the world's leading device manufacturers and equipment suppliers three times a year to discuss the business and economic issues facing the semiconductor industry, and how the two sectors can best cooperate to resolve them. The IEF discussions have spawned industrywide cooperative initiatives such as Industry Economic Modeling, including academic research and the Global Economic Symposia/ Workshops, and ISMT's new e-Diagnostics program. A new focus in 2001 may lead to a set of projects jointly sponsored by chipmakers and suppliers aimed at resolving some of the key industry challenges at the interface of business and technology.

ISMT's relationships with Selete, a Japanese consortium, broadened and deepened during the course of 2000. Continued cooperation on a host of 300 mm-related projects, coordinated by Randy Goodall, MM&P associate director, and his team, led the way to new joint projects in the critical area of lithography masks, and, perhaps more significantly, to a series of Boardto-Board discussions on broader areas for future collaboration between the two consortia.

A long-standing relationship with the Semiconductor Research Corporation (SRC) continued to flourish, epitomized by the extension of the Front End Processes (FEP) Research Center for an additional two years. Under the leadership of Ed Strickland, External Research and International SEMATECH/SRC FEP Research Center program manager, the Research Center pools the talents of technologists from nine universities, the two consortia and their members, and equipment suppliers to discover solutions for the continued scaling of transistors.

In July, ISMT and IMEC, the Belgiumbased research center, signed a joint research and development agreement to develop a new gate stack process for sub-100 nm semiconductor devices. This unprecedented multi-year, multi-million dollar international partnership represents a commitment to accelerate—by as much as two years—efforts to meet the ITRS gate stack/high-k requirements. Teams from both ISMT and IMEC worked long and hard through a series of complex issues to reach this agreement; for the first time ISMT assignees are working outside the United States.

A host of other cooperative projects with research labs, universities, consortia, and suppliers are also under way to realize the Roadmap: the standards program, under the direction of Jackie Ferrell, Guidelines and Standards program manager, continues to drive for industry consensus; work on equipment and process development continues with the Fraunhofer Institutes and with ASET; the ESH Division, represented by Jerry Chen, partners with universities in the Engineering Research Center for Environmentally Benign Semiconductor Manufacturing. Through all the various partnerships, ISMT works to keep its members and the industry on time, on target, together.

# Highlighting the Year's Accomplishments

Thanks to the vision, support, and direct involvement of the member companies, 2000 was a year of achievement for International SEMATECH (ISMT). Each of the technical divisions and support programs played a part in realizing the Roadmap, and each shared in ISMT'S overall success. The following pages of this annual report chronicle the details; here are a few highlights.

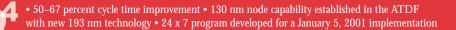

## 91% of Deliverables Met On Time

Even in the face of an ever-accelerating Roadmap, International SEMATECH's technical programs continued to progress well. 91 percent of the master deliverables were delivered to the members on schedule, the highest level ever achieved by the consortium, and 97 percent were completed by year-end. **157 nm Lithography**

Through specific programs focused on the micro exposure tool and material development and testing, and through a series of global meetings designed to build consensus, ISMT has built enough confidence in 157 nm technology that the whole industry is now supporting the introduction of 157 nm at the 70 nm node. Members can be proud of the consortium's pioneering effort in laying the groundwork for this important technology. Gate Stack and Ultra Shallow Junction

New gate stack materials and the ultra shallow junctions needed to extend planar

CMOS beyond 70 nm were the focus in Front End Processes; an important achievement was the delivery to our members of the first set of transistor data using high-k dielectrics. Excellent progress was demonstrated on high-k materials, metal gate electrodes, and ultra fast annealing techniques. Low-k Materials

Interconnect continued to offer significant value to members through its work on very low-k materials and very thin barrier layer technologies. Key to this success was the successful integration of a two-level dual Damascene process using a porous low-k dielectric. e-Diagnostics

Ramped up at "Internet speed" this year at the request of ISMT's Board of Directors and the Industry Executive Forum, the e-Diagnostics program attracted industry-wide participation and made great strides in driving pre-competitive technology and open standards in this emerging field.

### Metrology/Yield Management Tools Initiative

International SEMATECH and leading tool suppliers brought together an array of metrology and defect detection tools to spur the development and evaluation of new technologies to characterize masks, measure process variation, and ensure product quality.

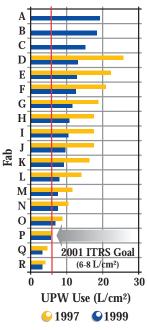

#### **Resource Conservation**

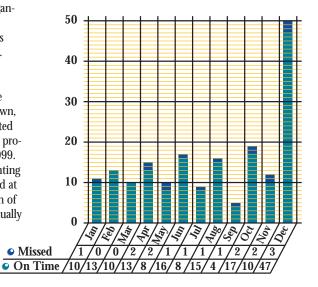

For a relatively small program, ESH packs a large punch, having been instrumental this year in initiatives to reduce water use and energy consumption in production facilities. ATDF Cycle Time and 300 mm Support

Focusing on cycle time and customer satisfaction has improved the throughput of the Advanced Technology Development Facility (ATDF) by a factor of three. Moreover, member companies have benefited from the ATDF's increasing 300 mm support capability; this year the ATDF supplied over 7,000 300 mm wafers to member companies starting up their pilot lines, helping to accelerate the critical time window between tool acceptance and wafer starts.

ISMT's success in 2000 was broader than just these highlights. It involved a whole host of technical projects, as well as initiatives implemented by the various support services organizations to keep the consortium both effective and efficient. ISMT's achievements are a result of the dedication and hard work of many people—employees, assignees, member companies, and global partners—all working together to realize the Roadmap.

(above L-R) Rich Harbison, 157nm Program Manager Gene Feit, Resist Development Manager

(above L-R) Gerhard Gross, Director of Lithography Wally Carpenter, Mask Strategy Program Manager John Canning, NGL Program Manager

## Lithography: Leading Technology Acceleration

International SEMATECH (ISMT) continues to lead the development of future solutions for the rapid acceleration of the lithography technology nodes for the worldwide semiconductor industry. The acceleration of the technology nodes outlined in the International Technology Roadmap for Semiconductors (ITRS) provides opportunities-and poses challenges-to ISMT's role in guiding the industry in developing processes and materials leading to the manufacture of sub-100 nm devices. In 2000. International SEMATECH once again brought together global industry experts in various forums and symposia to unravel the complicated number of choices and challenges that must be overcome to reach a consensus on the direction of the next stage in lithography technology.

"We are providing strategic leadership for our member companies and for the industry," said Gerhard Gross, director of Lithography and an Infineon assignee. The work at International SEMATECH includes the support of suppliers and infrastructure development for all aspects of lithography so that member companies receive from their International SEMATECH membership a technology "package" that will meet their lithography needs. "What's a scanner without resist?" said Gross. "You need it all. and we investigate the entire lithography package. International SEMATECH is driving the development of the technology and infrastructure for future lithography."

(right)

ISMT members ranked and identified key 157 nm challenges at the 157 nm technical data review in November.

Of the six key focus areas identified by the International SEMATECH Executive Steering Council (ESC), two—Post 193 nm Technology and Mask Cost and Availability reside within the Lithography Division. Consequently, ISMT's advanced lithography work (Post 193 nm Technology) concentrates on two areas: pushing optical lithography, including 157 nm, to and possibly below the 70 nm node, and driving global consensus on Next-Generation Lithography (NGL) options and timing.

"In our 157 nm and NGL approaches we are leading the world. Our efforts have provided member companies with the first 157 nm evaluation tool," said Gross. The Exitech 157 nm microstepper installed in ISMT's fab is used by suppliers in the development of production-worthy resists. Gross adds that a planned insertion in 2003 of the EUV Micro Exposure Tool will provide member companies with a similar capability in today's mainstream NGL technology.

Timing in lithography is one of the major and most critical tasks that International SEMATECH is tackling for its members and the industry. "We are supporting the development of the infrastructure for the upcoming technologies in a shorter time period than we have ever faced before," said Gross. Key accomplishments and challenges within Lithography in 2000 helped to define more tightly the direction needed to deliver the technology on time, at the right node. **157 nm Lithography**

Three years ago, 157 nm technology was not considered an option for the extension of optical lithography. Today, as a result of ISMT's work on behalf of its members and the industry, 157 nm technology will likely take the industry to the 70 nm node. "Because of International SEMATECH's technology leadership, there are few, if any, obstacles left to prevent 157 nm lithography from becoming a reality," said Rich Harbison, 157 nm program manager.

ISMT is working in each of these areas identified in the table below, often in conjunction with material suppliers. For example, the consortium and vendors are testing new pellicle materials that not only have the required transmission at 157 nm, but more importantly.

| Critical | Critical Issues Facing 157 nm Development         |  |  |  |

|----------|---------------------------------------------------|--|--|--|

| ⊖ Re     | eticle defect control                             |  |  |  |

| ⊖ Re     | esist capability for 100 nm (practical thickness) |  |  |  |

| 😜 Ti     | ming/risk of production tools for the 100 nm node |  |  |  |

| 😜 Ca     | alcium fluoride for lens materials                |  |  |  |

| € Co     | ontamination control of the optical path          |  |  |  |

| ⊖ At     | tenuated phase shift mask material                |  |  |  |

| ⊖ Co     | ost of ownership                                  |  |  |  |

## 8

## Lithography (continued)

also have sufficient resistance to high-energy radiation so that they do not darken after multiple exposures.

### Resist

International SEMATECH took delivery in 2000 of the first 157 nm lithography microstepper from Exitech Ltd., and within weeks ISMT achieved performance levels equal to or better than those of its 193 nm microstepper. Without resorting to phase shift masks, 1:1 line and space patterns were resolved at 110 nm and 1:1.5 line and space patterns were achieved at 90 nm.

"This represents a tremendous boost to the continuing momentum of 157 nm technology," said Gene Feit, manager of Resist Development. ISMT plans to have prototype resist materials available by the end of 2001 and manufacturing quality material ready by the end of 2003. The microstepper is available for use by suppliers and member companies at ISMT's Resist Test Center (RTC) housed in the Advanced Technology Development Facility (ATDF). Significant progress has been made in developing new polymer backbones, which will provide sufficient transparency at 157 nm to allow reasonable resist thicknesses to be used for single laver resists. In addition, work continues on thin layer imaging and bi-level resists.

In 2Q 2000, 193 nm resist benchmarking was completed. The final report gave member companies a clear picture of both the state-of-

the-art and areas in need of improvement. The 193 nm resist activities were transferred to the Patterning program at the end of 2000. Patterning will continue to extend current 193 nm technology further than technologists have historically thought possible. Next Generation Lithography (NGL)

At the fourth NGL Workshop sponsored by International SEMATECH in September, the world's leading lithographers recommended that the worldwide industry narrow the NGL options to Extreme Ultra Violet (EUV) and Electron Projection Lithography (EPL).

"International SEMATECH's workshop builds global industry consensus on the NGL options, and that becomes increasingly important as NGL technology moves out of the R&D arena into the supplier area, where the entire infrastructure for this new technology is created," said John Canning, NGL program manager. "Commercial equipment suppliers are increasing their involvement in NGL through prototype tools planned for completion as early as year-end 2003," said Canning. "However, there still remain fundamental critical issues that require increased R&D efforts before these two approaches can get the full industry goahead for insertion at the 70 nm node." ISMT is addressing those critical issues in EUV and EPL through 13 projects, ranging from defectfree EUV mask blanks and EPL mask manufacturing on thin membranes, to high NA

optics manufacturing for the EUV Micro Exposure tool.

Mask Cost and Availability

During the past decade, the ITRS has been continually accelerated as the industry has found ways to improve lithography faster than expected. Much of this improvement has come from the ability to use sub-wavelength imaging techniques, including optical proximity correction and phase shift masks. However, these techniques place an increasing demand on the masks themselves both in terms of feature sizes and in materials and process complexity. For example, the effect on CD uniformity has been most pronounced with the target specifications pulled in by as much as five years earlier than defined just two years ago. These challenges have resulted in lower yields, higher costs and unacceptably long mask manufacturing times. In addition, the advent of 157 nm exposure tools requires changes in the mask substrates and the phase shifting materials. To ameliorate these challenges, ISMT has initiated a number of active programs with mask processing tool vendors in the area of write, inspect and repair, programs designed to improve yield and throughput, and to handle the more aggressive plans for improved resolution and optical enhancement techniques.

"Our strategy is to mitigate the risk those challenges pose by evaluating the most significant options for our members and driving for ►

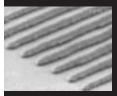

(above) 110 nm 1:1 line and space patterns

(**above**) 90 nm 1:1.5 line and space patterns

##

• Delivery of the first 157 nm lithography microstepper from Exitech Ltd.

• Fourth NGL Workshop sponsored by International SEMATECH builds global consensus

• 1st International Symposium on 157 nm Lithography held • 1:1 line and space patterns were resolved at 110 nm and 1:1.5 line and space patterns were achieved at 90 nm on the 157 nm microstepper • 193 nm resist benchmarking completed

• 13 projects launched on EUV and EPL Critical issues • Alternating PSM inspection project launched

• 157 nm Technical Data Review reprioritizes critical issue list

## **Electronic Voting Speeds Decision-Making**

Over the last three years, International SEMATECH (ISMT) has used an electronic decision support system that allows for anonymous votes, real-time results, and sophisticated graphing and ranking that gives members a clear picture of critical projects and key issues. With projects as complex as those at ISMT, the ability to compare and rank various projects against one another is crucial in decision making.

"It's very important for International SEMATECH to understand what our thirteen member companies consider critical," said Walter J. Trybula, manager of Productivity and Support in Lithography. Although other ISMT divisions, such as ESH, use the decision support system, Lithography initiated and heavily employs its use at various technical workshops and advisory group meetings.

A major advantage of the system is the anonymity it allows participants. In the past, voters walked to the front of a meeting room and stuck adhesive dots onto paper flip charts that contained the various choices up for consideration. Because of cultural differences among member companies, some company representatives were uncomfortable with the public nature of their vote. "This decision support system permits everybody to have an equal but anonymous voice," said Trybula.

The system has been used in ISMT's Next Generation Lithography workshops and 157 nm meetings, as well as in the Lithography, ESH, and Patterning program advisory groups.

"We can cover a tremendous amount of material in a relatively short period of time. This process is at least six times faster than using the sticky dots," said Trybula.

## Lithography (continued)

the most cost-effective solutions," said Wally Carpenter, Mask Strategy program manager and an IBM assignee.

According to Carpenter, new mask-making equipment—technologically ahead of the need—is required to get mask yields up. That effort drives very aggressive and potentially expensive equipment development programs. "That's where International SEMATECH plays a critical role, by subsidizing those equipment development costs and effectively 'buying time.' Equally important, through our programs International SEMATECH members provide suppliers with clear industry direction," he said. Major developments in 2001 will include the availability of the ETEC Mebes X write tool for 130 nm capability, the KLA DUV inspection tools, and the RAVE repair beta tool. With delivery expected by 4Q 2001, the RAVE mask repair tool will provide ISMT member companies with a new and innovative technology. "With these tools in place, we will be able to test the masks, inspect them and equally critical—repair them if defects are found, at yields that will keep masks affordable," said Carpenter.

International SEMATECH is also working in collaboration with Selete, a Japanese consortium, to address mask handling infrastructure changes, both for mask-makers and inside production facilities. The steps required to bring 157 nm mask capability to the industry call for a global approach. ISMT and Selete are addressing mask issues through collaboration on blanks transmission, surface contamination, and electrostatic discharge (ESD).

Recent delays in delivery of crucial mask equipment have caused IC manufacturers to consider maskless lithography, and ISMT is exploring the benefits and drawbacks of such an approach. Maskless lithography will be added to the agenda of the fifth NGL workshop hosted by ISMT in August 2001. "We must have a back-up plan in the event that we are unable to overcome the challenges involved in using masks. We need a strategy that will bring us to the 50 nm node and below," said Gross.

#### (below)

Top preferences for technology nodes among NGL Workshop participants.

| Narrowing the NGL Options |                                   |  |  |  |  |

|---------------------------|-----------------------------------|--|--|--|--|

| 130 nm                    | 248 nm optical and 193 nm optical |  |  |  |  |

| 100 nm                    | 193 nm optical and 157 nm optical |  |  |  |  |

| 70 nm                     | 157 nm optical, and EPL and EUV   |  |  |  |  |

| 50 nm                     | EUV and EPL                       |  |  |  |  |

| 35 nm                     | EUV                               |  |  |  |  |

#### (left)

The key elements of the decision support system are the computer with the controlling program, a transceiver for receiving the radio signals, and the handhelds with a keypad for selection of a voting choice. The computer screen shows the ranking of project importance by compiling the individual votes cast. As the use of these tools becomes more widespread, additional features can be employed to increase the decision making support available to the member companies.

Front End Processes: Focusing on the "Grand Challenge"

As semiconductor devices continue to shrink, the processes and materials used to make them are rapidly approaching their physical limits. To take full advantage of the reduced design rules of the International Technology Roadmap for Semiconductors (ITRS), the industry must move to thinner gate dielectrics for sub-70 nm devices. Silicon dioxide, which has been the heart of the MOS transistor for the last 40 years, is unable to perform to ITRS requirements at thicknesses at or below 1.5-2 nm because of excessive leakage and reliability problems. The ITRS calls for new dielectric materials to replace silicon dioxide; transistors using these high-k dielectrics are projected to enter manufacturing by 2005.

This year International SEMATECH (ISMT) delivered to its member companies the first set of transistor data using high-k dielectrics, a major step toward achieving a fully integrated high-k transistor. "This data puts our member companies and the industry on the right track in finding a replacement for current gate stack materials," said Mike Jackson, director of Front End Processes (FEP). "We're now in a position to make real life, conventional planar CMOS transistors using high-k materials. By bringing in suppliers at this stage, we will guide the industry to worldwide consensus for these new materials to ensure that we have ideal process equipment for manufacturing."

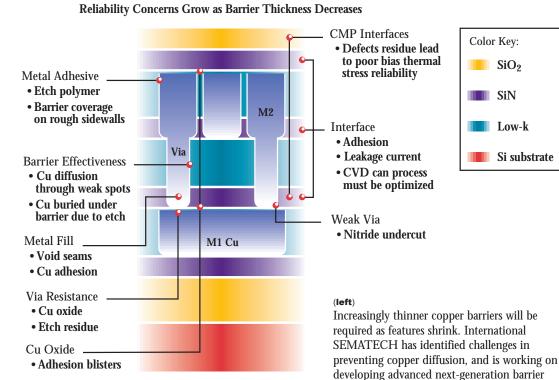

Among the topics covered in the report are the thermal stability of high-k materials, effective dielectric constant, leakage current, and integration. "We are moving away from something  $[SiO_2]$  that has been used for 40 years, and it's a real challenge," said Jackson. "How these materials behave when combined in conventional CMOS processes is one of the big questions that we are helping to answer," he said. For example, if annealed at too high a temperature, some materials lose their high-k characteristics. "Such integration issues," said Doping Program Manager Larry Larson, "represent the key challenge in manufacturing transistors of the future." Newly Acquired Equipment Gives International SEMATECH Capability to Deposit Candidate High-k Materials

In the past, high-k development has been limited by the availability of deposition systems to produce the layers to be tested. This limitation has been overcome with the acquisition of the Applied Materials MOCVD chamber and an ASM ALCVD chamber. Moreover. ISMT will benchmark other tools and techniques in coordination with IMEC, the Belgium-based, government-supported research institute, and the Fraunhofer Institute. "Our strategy is to accelerate that movement from the research state right into production," said Jackson. "Having a flexible set of tools provides us with different techniques, so if IMEC or the FEP Research Center recommends an alternate material, we can test it for manufacturability." 100 nm Technology Ultra-Shallow Junctions Demonstrated

Using low energy ion implantation and spike annealing, ISMT has been able to get to 100 nm and 70 nm node requirements for ultra shallow junctions. The ITRS requires junctions of 250 Å for the 100 nm technology node. Due to an effect called transient enhanced diffusion, any implanted junction occurs at least at that depth when annealed. "The challenge involved in this is to discover implant and anneal techniques that can provide shallower junctions than allowed by this effect," said Larson. "It is important to realize that forming junctions and finding a high-k material system cannot happen independently. The most challenging of the issues facing FEP is delivery of ultra shallow junctions and high dielectric constant in the same manufacturingworthy transistor flow."

Because it appears that implant and anneal techniques will not work at the 50 nm node, ISMT has begun a major activity looking at alternative methods of producing shallower junctions.

### Gate-quality Silicon Nitride Benchmarked

Nitride-based dielectrics are used now as one of the primary dielectric systems in the manufacture of transistors, and will remain the system of choice until an acceptable, manufacturing-worthy high-k dielectric is developed. Consequently, benchmarking silicon nitride has immediate benefits to our member companies. A study conducted at the University of California at Los Angeles for International SEMATECH found that nitridation of a furnace or rapid thermal processed (RTP) silicon dioxide by remote plasma nitridation (RPN) is feasible. Compared to plasma-nitrided oxides, silicon nitride films deposited by rapid thermal chemical vapor deposition (RTCVD) have several drawbacks. These RTCVD nitride films >

(above L-R) Mike Jackson, FEP Director Larry Larson, Doping Program Manager

(above L-R) International SEMATECH demonstrated the consortium's first working PMOS transistors with Laser Thermal Anneal (LTA) in August 2000. **FEP** (continued)

## **Planar CMOS Grand Challenges**

Based on the 1999 International Technology Roadmap for Semiconductors (ITRS)

generally require multi-step processing—as many as four steps in the better-performing films—that can significantly reduce process throughput. In addition, there is generally a trade-off between the achievable equivalent oxide thickness and transistor mobility.

Plasma-nitrided oxides have exhibited an order of magnitude lower gate leakage current and comparable saturation current to pure oxides. Only a small degradation in device mobility—three percent for PMOSFETs and seven percent for NMOSFETs—with plasmanitrided gate dielectrics has been observed. In contrast, RTCVD nitrides can lead to more than 50 percent degradation in transistor mobility for an equivalent oxide thickness (EOT) of approximately 1.4 nm. An EOT of about 1.4 nm has also been achieved using the RPN process. Mobility data on these films is currently being collected.

"People are really interested in high-k materials, but you don't need them today," said Jackson. "This work has helped delay the need for high-k materials to the 100 nm node or beyond."

#### 100 nm Technology Modeling

In 2000, FEP established a modeling tool that both demonstrates 100 nm technology and allows discussions with suppliers and other **>**

Benchmarked gate quality silicon nitride tools and techniques

Key report on high-k dielectric material selection issued by the FEP-RC

Benchmarked ultra-shallow junction high ramp rate spike anneals

FEP Highlights

## **FEP** (continued)

members without divulging company-specific information. The model gives members and suppliers the means to conduct manufacturing cost sensitivity analyses. "This allows our members to understand MOS device challenges and prospective performance at the 100 nm node," said Peter Zeitzoff, an ISMT fellow who focuses on process integration and NMOS device optimization. "Our member companies can project the main challenges and possible solutions in performance and manufacturing sensitivities for MOS devices at the 100 nm node."

The modeling analyzes the impact of the physical thickness of the high-k gate dielectric on short channel effects. Moreover, the model helps drive the process control requirements of the ITRS, since input from the International SEMATECH model feeds directly into the ITRS working group deliberations. "By helping our member companies gauge how sensitive the changes will be in the main parameters of device making at the 70 nm node, we set industry direction," Zeitzoff said.

While International SEMATECH is working toward a high-k material, if that solution is found to be unsuitable to the gate stack challenge, alternatives to high-k materials must be quickly explored and developed. "What if you don't have to use high-k materials, but

B could use a different structure and still meet Moore's law?" asked Jackson. Because of International SEMATECH's relationships with other research institutes and universities that are exploring alternative ways to meet performance requirements, ISMT will have first access to such structures, and can evaluate their feasibility on behalf of its member companies. "There are a lot of smart people who could come up with an alternative device structure that will let you use silicon oxide," he said.

"Nevertheless," said Jackson, "International SEMATECH is moving forward rapidly to achieve the right high-k dielectric for future gate stack." To take advantage of gate stack research available worldwide, International SEMATECH this year signed a joint research and development agreement to pursue a new gate stack process for sub-100 nm semiconductor devices with IMEC.

This multi-million dollar international partnership represents a major commitment to accelerate—by as much as two years—efforts to meet the requirements of the ITRS to find a

**Critical Issues**

#### **A** Isolation STI Fill

- **B** Low R<sub>s</sub> Contact Leakage

- **C** "Dual" Metal Gate <100nm Node

- D CD Control 65nm 2003 Etch

- **E** Gate Dielectric: mid-k < 25 nm; high-k >20 nm—Tunneling/Reliability

- **F** USJ Extension ~200Å @ 100nm Concentration/Abruptness

- **G** Contact Junction Depth 400Å 2003

- **H** Channel Doping Steep Retrograde

(above)

A depiction of the key front end process challenges as CMOS is scaled. International SEMATECH is focusing its efforts in FEP on high-k materials, ultra shallow junctions, and the total process integration into a CMOS transistor.

First high-k transistor build completed

IMEC high-k program initiated

Acquired AMAT MOCVD tool that gives ISMT capability to deposit high-k materials

• FEP-RC contract extended from three to five years

D

**(F)**

## **FEP** (continued)

replacement for current gate stack materials.

"This allows International SEMATECH access to outside information, to bring it back into International SEMATECH, and assess its feasibility," said Ed Strickland, a Motorola assignee who serves as program manager for external research and heads the FEP Research Center. The project involving IMEC focuses on advanced gate stack material deposition tasks, electrical/reliability characterization, and replacement transistor gate development for materials characterization, ESH and contamination control. The project will, for the first time, involve placing ISMT assignees outside the U.S.

"We are reaching out to international centers of excellence so that our member companies will achieve their goals," said Jackson. "IMEC provides a crucial piece of the puzzle that will complete the move to new gate stack technology. By leveraging funds through the SRC (Semiconductor Research Corporation) and IMEC, International SEMATECH reduces the risk for its members, and accelerates that knowledge back to our member companies."

ISMT continues to work with the SRC through the FEP Research Center and U.S. universities on fundamental research, and also with equipment suppliers from the U.S., Asia, and Europe. "With our global interactions, we call on the world's resources to help us build a complete set of data on which to help guide the industry to a gate stack replacement," said Jackson.

## FEP Research Center Moves Closer to High-k Solution

A key link to overcoming the technical challenges necessary for the continued scaling of transistors, the FEP Research Center (FEP-RC) moved forward in two crucial areas during 2000. The first was the narrowing of the choices for high-k dielectrics to three materials. "This enabled researchers to produce actual operating transistors using these new high-k materials and allowed them to begin to characterize these transistors and their operating parameters," said Ed Strickland, program manager of the FEP Research Center, and a Motorola assignee.

The second breakthrough for researchers was the production of very shallow doped junctions using selective epi deposition. "The significance of this discovery is that very shallow junctions can be formed with high concentrations of dopants—higher than possible with current doping processes," said Strickland. High-k and ultra-shallow junctions are two of the three major building blocks to enabling the industry to scale transistors to smaller than 70 nm. "The researchers of the FEP-Research Center are definitely working on the leading edge of these fields. Without these solutions from the Research Center, the industry will not be able to continue to scale transistors smaller and smaller," said Strickland.

"The FEP Research Center has proven to be the best example of

cooperative research in the world today," said Martin Giles of Intel and Semiconductor Research Corporation (SRC) Industrial co-chair. "It has already delivered major research results in high-k dielectrics, gate electrodes, and shallow junctions."

A key ingredient to that success has been the excellent collaboration among the different researchers at the various universities. "That synergy among researchers is one of the truly imperative elements of this Research Center," said Strickland.

Established in 1998 in partnership with the SRC, the FEP Research Center is a leader in front end processes research. This cooperative effort, which includes nine U.S. universities, brings together technologists from International SEMATECH and the SRC, their member companies, and equipment suppliers.

"We are attempting to discover solutions for devices beyond 70 nm. We then feed that information back to ISMT. The FEP division then combines that data with process technology to provide an integrated approach to the challenge of scaling below 70 nm," said Strickland.

Set up originally for three years only, the FEP-Research Center was extended for two additional years to 2003. Research into gate electrodes will become a key focus in 2001.

(above) Ed Strickland, Program Manager, External Research and International SEMATECH/SRC FEP Research Center

# Interconnect: Narrowing the Options, Discovering New Challenges

As copper and low-k dielectrics replace aluminum and silicon dioxide in semiconductor manufacturing, International SEMATECH (ISMT) members look to the Interconnect Division to lead the effort to characterize and screen the many new materials and processes involved in this fundamental shift in interconnect fabrication, so the members can focus on the most promising. Equally important, ISMTs member companies rely on Interconnect working closely with suppliers on the resulting changes required in tools and materials. The Executive Steering Council (ESC) has identified low-k dielectrics as a critical focus area for International SEMATECH, and the Interconnect Division's long-term objective is to study advanced tools, processes, and materials in order to help ISMT members accelerate their use of copper, low-k, and Damascene processing down to 50 nm design rules. The division focuses on both technology development and tool improvement in its efforts to help member companies realize the aggressive interconnect technology roadmap.

The task is not easy. In theory, copper and low-k dielectrics can provide the performance gains the industry will need for the next two to three technology generations. Although copper metalization is moving into mainstream manufacturing, much remains to be done to extend barrier seed and fill technologies, to work with tool suppliers on measurement and reliability issues, and to study future copper scalability. The transition to low-k materials has proven to be far from smooth, given the inherent limitations in the materials themselves and the problematic ways in which these materials interact with manufacturing processes such as patterning, chemical mechanical planarization (CMP), and metalization.

In 2000, the Interconnect Division's major accomplishment was to develop processes and methods that led to the fabrication and electrical test of two-level copper structures in five low-k materials, including two porous materials. These two-level metal tests came after an initial round of physical and electrical evaluations of eight low-k dielectric materials through one-level metal electrical testing. "This is a significant achievement," noted Paul Winebarger, director of the Interconnect Division and a Motorola assignee. "In order to reduce an insulator's dielectric constant, some of the attractive physical properties associated with silicon dioxide will be sacrificed. Our job is to make known the advantages and limitations of these new insulator materials, and to help suppliers and our members develop robust manufacturing solutions to any of their intrinsic material shortcomings. Our work highlighted and gave better understanding to the many engineering tradeoffs that must be considered in the transition to these new advanced interconnect materials."

The various integration approaches evaluated by Interconnect this year were not always good-news stories. International SEMATECH sometimes found new challenges that the industry had not anticipated. Low-k/DUV resist poisoning, for example, was a new problem ISMT characterized extensively and then reported in detail to its members, giving them an informed alert on an unexpected issue.

"The fabrication of multi-layer copper interconnects using very low-k materials is proving to be a significant challenge," said Ken Monnig, associate director of Interconnect. "We are learning that it will not be possible to solve these issues by engineering the low-k material alone. Significant engineering will be required in etch, post-etch clean, lithography, CMP, and metalization technology, as well. International SEMATECH has been a pathfinder in bringing these issues to light and providing first-pass solutions to give our members a head-start on their internal product learning curves."

Given this degree of interaction and interdependence among the various technologies, it is not surprising that the activities and programs of the Interconnect Division are highly interrelated.

#### **Copper Metalization**

The Copper Metalization program aims to ensure a capable tool and material infrastructure for copper processing. This year's emphasis was on advanced copper barrier and copper seed materials, and their deposition techniques. "Last year we benchmarked the processing capability of most of the PVD [physical vapor deposition], CVD [chemical vapor deposition] and electroplating tools used for barrier, seed, and fill," said Klaus Pfeifer, the Copper Metalization program manager and a Philips assignee. "This year we turned our attention to working with suppliers and universities to identify and characterize advanced CVD copper **>**

(above L-R) Ken Monnig, Interconnect Associate Director Paul Winebarger, Interconnect Director

(above L-R) Bob Havemann, Module Integration Program Manager Klaus Pfeifer, Copper Metalization Program Manager Shin Kook Lee, CMP Program Manager Jeff Wetzel, Low-k Dielectric Program Manager

## **Interconnect** (continued)

seed and barrier materials." The copper team conducted electrical via resistance evaluations of four CVD and one ALCVD (atomic layer chemical vapor deposition) copper barrier materials (including TiN, TiSiN, WN, TaN) on dual Damascene structures.

Increasingly thinner copper barriers will be required as feature sizes shrink, and this group continued its work with universities—including The University of Texas at Austin—on the development of advanced next-generation barrier materials, which will ultimately be evaluated for their commercialization potential. The Copper program also continued its efforts to squeeze maximum performance out of copper integrated circuits and foster new solutions for future feature size reductions, by characterizing copper scalability down to 80 nm and

materials that will ultimately be evaluated for

their commercialization potential.

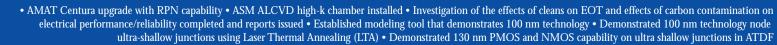

## **Preventing Copper Diffusion Creates Challenges**

looking closely at the effect of line width on copper resistivity. Low-k Dielectrics

Evaluating new low-k dielectric materials and improving supplier capability are the key objectives of ISMT's Low-k Dielectric program. Facing such issues regarding low-k dielectric (<2.5 k) materials as dielectric constant stability, integration-induced damage, resist poisoning, etch/clean damage, adhesion, and CMP damage, the program seeks to develop a mechanistic understanding of these various materials issues and then to feed this information as quickly as possible back to suppliers to drive improvement, and on to the members to help guide their materials decisions. "Providing the member companies with our physical and electrical characterization data allows them to make more informed decisions about which materials they wish to investigate further," said Jeff Wetzel, Low-k Dielectric program manager on assignment from Motorola. "This gives them early warning on incompatibilities between materials, processes, and the current tool set." In addition to the one-level metal and two-level metal characterizations performed on various low-k materials, with a special emphasis on porous materials, the low-k and CMP groups also established CMP capability on porous low-k films and supported the etch group to complete electrical characterizations of plasma etch/clean and wet cleans on >

• Began one level metal characterization of eight low-k materials

## **Interconnect** (continued)

low-k materials. The low-k group continues to benchmark and improve promising low-k dielectric CVD deposition tools. Module Integration

The Module Integration program expands on the low-k evaluations and quickly identifies the initial problems encountered in building structures in a number of selected immature low-k materials with copper Damascene processing. In 2000, the module integration group performed integration/reliability characterizations of new low-k dielectrics and ultra-thin CVD/ALCVD metal barriers in single and dual copper/Damascene structures. The group fabricated working multi-level metal test vehicles and used those structures to test interand intra-level electrical properties, as well as to provide data on high frequency and reliability characteristics of advanced low-k materials. Barrier evaluations included physical characterization (step coverage, adhesion, texture) as well as electrical parametric and reliability testingfor bias thermal stress and electromigration-in integrated dual Damascene structures. According to Bob Havemann, Module Integration program manager and an assignee from Texas Instruments, such efforts serve to detail the interactions of new processes (dual Damascene, plating), materials (copper, barrier, low-k dielectrics) and tools. "This is important information that our members need to support their future technology decisions," stated Havemann.

## Chemical Mechanical Planarization

The Chemical Mechanical Planarization (CMP) Program focuses on copper Damascene polish, and works to accelerate CMP consumable development, determine baseline processes, and evaluate unique tools, which may provide more revolutionary approaches to improving CMP capability. In its work this year on CMP/low-k integration and exploring interactions between CMP and new copper barrier materials and copper deposition techniques, the CMP group dealt with issues such as dishing, copper-to-barrier selectivity, selectivity to underlying dielectric, and defectivity.

"As the industry moves to fragile, porous low-k materials, our responsibility is to help create core competency in Damascene polish over porous low-k," said Shin Kook Lee, CMP program manager and senior assignee from Hyundai. "Not only will we work in-house on process development, but we'll also continue our efforts to catalyze suppliers of pads and slurries to address this issue, and we'll work with supplier companies pursuing mainstream polishing solutions and alternatives such as spin etch or electropolish."

In 2000, the group continued to benchmark and evaluate copper CMP tool suppliers in an effort to accelerate development and identify new equipment approaches that will increase productivity and cost-effectiveness. Cost is a concern: as circuit designers use more levels of metalization, lowering the cost of CMP becomes more critical.

In 2001, Interconnect will focus on three challenges: delivering early evaluations of potential low-k dielectric materials with compatible barrier solutions for the 100/70 nm node; demonstrating candidate low-k barrier solutions with a two-level metal integration process, including baseline reliability; and developing and demonstrating viable Cu/low-k CMP processes for porous low-k materials.

The industry faces a critical challenge in realizing the Roadmap as it considers the next steps in interconnect, after copper and low-k. This so-called "brick wall" looms on the horizon, and in fact, the limits of copper/low-k material capability are not too far away from ISMT's current activities. No known solutions currently exist after the transition to copper and low-k materials. Invention is needed, as is coordination with the design and architecture community that will no doubt contribute to the ultimate solution. ISMT will continue to promote industry coordination in tackling this serious potential show-stopper for discovering new improvements in integrated circuit performance.

(above) The Novellus INOVA<sup>®</sup> is an advanced copper barrier/ seed deposition system supporting International SEMATECH's dual Damascene technology.

(**above**) Two-level metal dual Damascene results represent the first successful integration of a k=2.2 material.

• Evaluated performance/reliability of lower-k dielectric barrier(s)

Completed integration of four low-k dielectric materials through two level metal

Final report on 2000 CVD copper fill activity and benchmarking activities

Completed screening of three seed repair chemistries

• Established CMP capability on porous low-k films • Evaluated electrical via resistance of four CVD and one ALCVD Cu barrier materials on dual Damascene structure • Completed characterization of Cu scalability down to 80 nm • High-frequency characterization of low-k materials and interconnect waveguide structures • Performance, reliability, and packaging assessment of Cu/low-k (k<2.5) material #1

(above) Gil Shelden, Patterning Program Manager

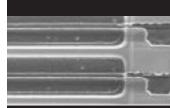

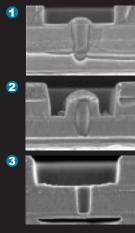

Via resist poisoning at the subsequent trench photo step (via first approach). Resist poisoning has been observed on a variety of low-k dielectrics.

2 Via poisoning of resist after the trench etch step. A "volcano" surmounts the via.

3 A dual top hard mask approach has been used instead of the via first approach to eliminate the resist poisoning problem.

# Patterning: Extending 193 nm Technology

October 1, 2000 marked the operational debut of the Patterning program, drawing together in one cross-functional program activities which had been spread across Interconnect, Lithography, and the Advanced Technology Development Facility (ATDF). Now the champion for International SEMATECH's (ISMT's) 193 nm Extension key focus area, the Patterning program's overall objective is to ensure that the 193 nm/157 nm technology is ready on time, and is a viable and cost-effective answer to next-generation feature requirements.

"193 nm patterning is now the majority choice for the 90 nm node (2004)," said Gil Shelden, Patterning program manager. "And it will likely be pushed farther as the ITRS accelerates. The new Patterning program offers unified direction in our effort to stay on the 193 nm productivity curve as long as possible." **Optical Extension**

ISMT's Optical Extension program emphasized three 193 nm process development and enhancement techniques:

• Resist Performance—Currently available resist materials need more characterization and performance improvements in etch resistance and selectivity; edge roughness, material stability, substrate compatibility, cost, and material availability remain manufacturing concerns. During the year, ISMT benchmarked 18 different 193 nm resists. Although excellent progress is being made, none of the currently available materials is suitable for 100 nm node production requirements.

**Patterning Highlights**

0.6NA 193nm SVGL tool installed and printing

• Obtained diagnostic data collection for C<sub>x</sub>F<sub>x</sub> species

Degradation of Optical Material—193 nm ArF Excimer wavelength technology requires development of special optical materials, since the higher energy of 193 nm illumination creates greater potential for material degradation. In 2000, ISMT completed accelerated life testing of 193 nm materials including pellicles and fused silica for mask blanks. Several promising materials have been identified, but concerns remain about induced birefringence. Phase Shift Masks (PSMs)—Preliminary testing of alternating and attenuated PSMs has made it clear that the technology still needs development, especially in the area of attenuated phase shift materials for contacts, vias and trenches. Alternating PSM technology, used extensively to improve isolated line (gate) critical dimension (CD) control, has limited benefits for dense lines and spaces.

#### Etch

The Etch group performed etch characterization of four low-k materials, investigated the root causes for the low-k/DUV resist poisoning phenomenon, and completed electrical characterizations of the impact of several plasma etch/clean and wet clean processes on low-k materials. Moreover, working closely with the Front End Processes (FEP) Division on how to etch the next generation of gate stack materials, the Etch group achieved initial 193 nm gate etch results for both SiO<sub>2</sub> and ZrO<sub>2</sub> gates. Going forward, the Etch Tools program will support key Interconnect, FEP, and Lithography initiatives by providing etch/cleans process and tool evaluations in three areas: low-k materials, advanced gate stack materials, and 193 nm resist patterning interactions. In 2000, the majority of this work was executed at 248 nm; in 2001, it is anticipated the work will extend to 193 nm. In addition to the challenges of smaller feature size and reduced depth of field, a new set of materials interaction challenges will emerge when dealing with new resist systems.

The Etch Chemistry and Diagnostics program focused its efforts on collecting diagnostic data for  $C_x F_x$  species and on extensive modeling of oxide etch rates in  $C_2 F_6$ . Next year this program will produce basic plasma chemistry database sets to support individual member company development of plasma modeling codes.

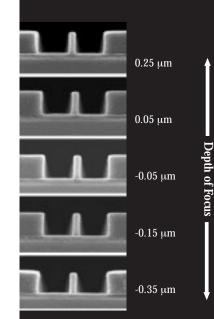

#### **ATDF/Tool Support**

Involved with the development of 193 nm technology since the early 1990s, ISMT received its first 193 nm limited field 0.6 NA microstepper in 1996 to support resist development. ISMT later partnered with DNS and obtained a state-of-the-art track system to interface with an SVGL MS193 full-field 0.6 NA 193 nm scanner. While dense contacts/vias continue to be the biggest challenge, standard binary reticles are currently producing 130 nm dense features with reasonable process latitude and depth of focus (0.6 µm); ISMT is achieving 100 nm gates with binary plates, and 70 nm gates with phase shift technology. ■

Delivered 3D EMF software; electrical characterization of several low-k clean processes

• 193 nm gate etch results obtained • completed etch characterization of four low-k materials • Low-k resist poisoning characterization initiated and analyzed

## **Metrology/Yield Management Tools:** Accelerating Innovative Solutions

During 2000, International SEMATECH (ISMT) launched a major effort to reduce the limitations facing future metrology and yield management technology by consolidating Lithography Metrology, FEOL/BEOL Metrology, and Yield Management Tools into a new, more focused Metrology/Yield Management Tools (M/YMT) Program. The program's critical objective is to ensure the availability of metrology and yield management tools for the 100 nm node and beyond, by accelerating the availability of metrology in CD (critical dimension), overlay, gate stack (high-k), ultra shallow junction, and low-k, and by accelerating yield management solutions in defect detection, yield modeling, and defect sourcing.

"New lithography capabilities for reduced feature sizes, plus the introduction of new materials such as low-k and high-k dielectrics, are pushing metrology toward innovative solutions," stated Alain Diebold, M/YMT technical manager. "For the industry to stay on the Roadmap, new methods of characterizing masks, measuring process variation, and ensuring product quality must be found." Ron Remke, program manager and a Lucent/Agere assignee, added, "As geometries shrink, we increase the detrimental impacts of defects, making defect detection, measurement, and characterization more important than ever."

Highlighting the year's efforts in M/YMT were significant improvements in the design, effectiveness, and precision of next-generation metrology tools, particularly in their ability to

interface with new processes and materials. M/YMT also spearheaded a set of vield management tool benchmarking, inspection and software projects designed to improve member companies' yields as rapidly as possible. Key achievements include:

- Optical models for measuring oxynitride and high-k materials for advanced gate stacks

- Specifications for a next-generation CD scanning electron microscope (SEM), developed in conjunction with four major suppliers

- Testing software designed to improve the resolution, precision, and 3-D capabilities of CD-SEMs, in cooperation with the National Institute of Standards and Technology (NIST)

- Testing reference wafers for a promising in-line junction depth measurement tool

- Benchmarking the defect inspection tools of six key suppliers, and developing a new reticle set to aid in evaluating defect inspection equipment

- Investigating the defectivity of low-k dielectric films and the ability of existing tools to inspect for defects on low-k films

- · Evaluating new software tools to identify particle-sensitive circuit areas

- Evaluating commercial software for defect mapping and image retrieval Metrology/Yield Management Tools Initiative

This new model of collaboration between ISMT and leading industry suppliers such as Therma-Wave, Boxer-Cross, Hitachi, KLA-Tencor, Philips Analytical, and Veeco, launched

during the summer, will help the industry surmount the critical metrology and yield management challenges posed by the International Technology Roadmap for Semiconductors (ITRS) by accelerating next generation processing through testing of new tools. "The Initiative provides suppliers with access to new technology generations and new materials," said Diebold. "Tools for in-line ellipsometry, in-line non-contact capacitance-voltage, in-line junction depth measurement, CD measurement, defect detection, and in-line measurement of seed copper/barrier thickness and CMP control are all involved in this groundbreaking cooperative effort to evaluate equipment at the 130 nm and 100 nm nodes, and to develop metrology and yield management capabilities for critical areas such as gate stack, low-k, and 193 nm optical extension."

#### Yield Council

ISMT's Yield Council is a long-standing member company forum that meets three times a year to share best practices in rapid yield learning and to benchmark yield improvement activities. "The most important thing you can improve in manufacturing is your yield, because that determines your profit margin and increases your capacity," stated Remke. "Over the many years of the Yield Council's existence, it has consistently rated near the top for member company value. Member companies report to us that the information and benchmarking results that they receive as part of the Yield Council are not available from any other source."

#### (above) Therma-Wave Opti-Probe 5240D with scatterometry capability

(above) Ron Remke. M/YMT Program Manager

(above) Alain Diebold. M/YMT Technical Manager

## **Metrology/YMT Highlights**

• Therma-Wave Opti-Probe operational Completed Critical Area Extraction (CAE) software assessment

Extended CD-SEM to 3D NIST software given to member companies

- NIST test of SRC Nanotip source for extending CD-SEM to future generations • Beyond CD-SEM—SRC electron holography proof of concept interim report