# **Digitally Controlled Audio Mixer**

### Description

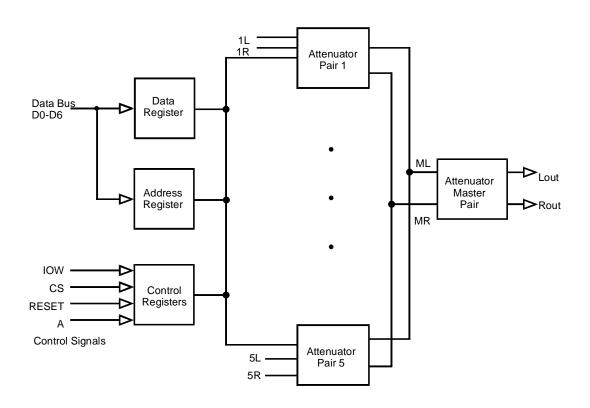

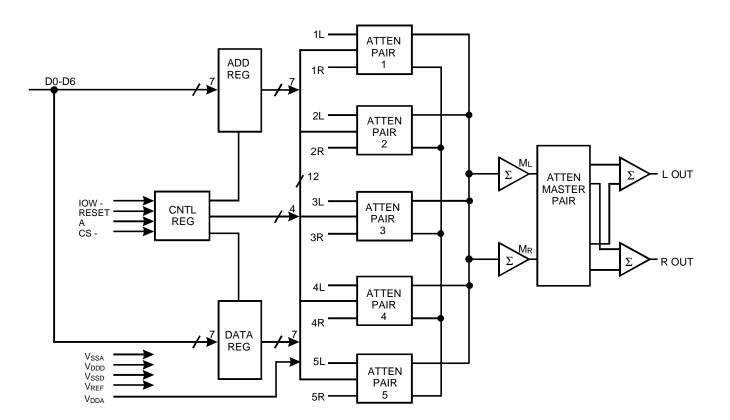

The **ICS2101** is a CMOS digitally controlled multi-channel line-level stereo audio mixer for use in multimedia applications. High performance attenuators provide precision gain control in -0.5dB increments. The ten input channels may be used as mono inputs, pairs of stereo inputs, or any combination of mono and stereo inputs appropriate for the application. Stereo balance and mono panning functions are fully supported. The **ICS2101** is compatible with the ISA industry standard bus.

### Features

- Five stereo input pairs

- One stereo output pair

- Precision gain control in -0.5dB steps

- Separate attenuation and balance control for each input pair

- Mono input mode with panning capability

- Master attenuation and balance control for output

- Low noise, low distortion

- ISA compatible

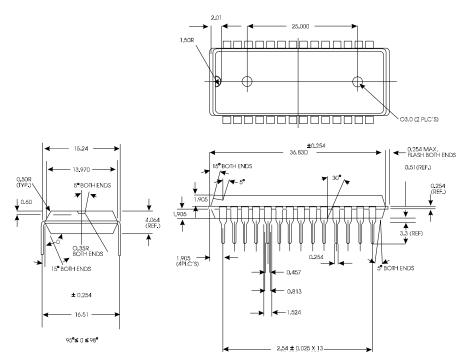

- 28-pin DIP or SOIC package

Figure 1 - Block Diagram

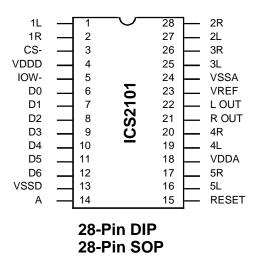

## **Pin Descriptions**

| 1                                       |                  |      |                                                                                                                              |

|-----------------------------------------|------------------|------|------------------------------------------------------------------------------------------------------------------------------|

| PIN NUMBER                              | PIN NAME         | TYPE | DESCRIPTION                                                                                                                  |

| 1, 2, 16, 17, 19,<br>20, 25, 26, 27, 28 | 1L-5L, IR-5R     | AI   | Audio inputs (left and right) for attenuators 1 through 5. An external coupling capacitor should be connected to each input. |

| 3                                       | CS-              | Ι    | Chip select, active low.                                                                                                     |

| 5                                       | IOW-             | Ι    | Input/output write, active low. Data is latched on the rising edge.                                                          |

| 6, 7, 8, 9, 10,<br>11, 12               | D0-D6            | Ι    | Data bus, active high.                                                                                                       |

| 14                                      | A                | Ι    | Address/data select. Low input selects the data register, high input selects the address register.                           |

| 15                                      | RESET            | Ι    | Resets all registers to OOH, active high.                                                                                    |

| 21, 22                                  | Rout, Lout       | AO   | Line level audio outputs.                                                                                                    |

| 23                                      | V <sub>REF</sub> | Р    | Reference voltage of $0.44V_{DDA}$ . A 1000 pf capacitor should be connected between $V_{DDA}$ and $V_{SSA}$ .               |

| 4                                       | V <sub>DDD</sub> | Р    | Digital power.                                                                                                               |

| 18                                      | V <sub>DDA</sub> | Р    | Analog power.                                                                                                                |

| 13                                      | V <sub>SSD</sub> | Р    | Digital ground.                                                                                                              |

| 24                                      | V <sub>SSA</sub> | Р    | Analog ground.                                                                                                               |

I=Input; O=Output; P=Power; A=Analog

## **Absolute Maximum Ratings**

| -65°C to 150°C                  |

|---------------------------------|

|                                 |

| -0.3V to V <sub>DDD</sub> +0.3V |

| 7V                              |

| 1W                              |

|                                 |

## **Standard Test Conditions**

Operating Temperature Range . . 0°C to 70°C Power Supply Voltage . . . . . . 4.75 to 5.25 Volts

### **DC Characteristics**

| $V_{DDD} = 5V$   | $V_{\text{DDD}} = 5\text{V} \pm 5\%, \text{ V}_{\text{SSD}} = 0\text{V}$ |      |                      |                  |       |                                                   |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------|------|----------------------|------------------|-------|---------------------------------------------------|--|--|--|--|--|

| SYMBOL           | PARAMETER                                                                | MIN  | TYP                  | MAX              | UNITS | CONDITIONS                                        |  |  |  |  |  |

| V <sub>IH</sub>  | Logical 1 Input Voltage                                                  | 2.4  |                      | V <sub>DDD</sub> | V     |                                                   |  |  |  |  |  |

| VIL              | Logical 0 Input Voltage                                                  | 0    |                      | 0.8              | V     |                                                   |  |  |  |  |  |

| IIL              | Input Leakage Current                                                    | -1   |                      | 1                | uA    | $0 < V_{IN} < V_{DDD}$                            |  |  |  |  |  |

| Іон              | Output Source Current                                                    | -100 |                      |                  | mA    | $V_{OUT} = V_{REF} + 1V$<br>Master attenuator off |  |  |  |  |  |

| Iol              | Output Sink Current                                                      |      |                      | 100              | mA    | $V_{OUT} = V_{REF} - 1V$<br>Master attenuator off |  |  |  |  |  |

| VREF             | Internal Reference V                                                     |      | .44 V <sub>DDD</sub> |                  | V     |                                                   |  |  |  |  |  |

| IADD             | Analog Supply Current                                                    |      | 7                    | 10               | mA    |                                                   |  |  |  |  |  |

| I <sub>DDD</sub> | Digital Supply Current                                                   |      | 10                   | 100              | μA    |                                                   |  |  |  |  |  |

## **AC Characteristics**

| SYMBOL           | PARAMETER                   | MIN        | TYP | MAX    | UNITS | CONDITIONS                                                                                    |  |  |  |  |

|------------------|-----------------------------|------------|-----|--------|-------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| ANALOG           |                             |            |     |        |       |                                                                                               |  |  |  |  |

| VAI              | Analog Input Voltage        | AC coupled |     |        |       |                                                                                               |  |  |  |  |

| AF               | Analog Frequency Range      | 20         |     | 20,000 | Hz    |                                                                                               |  |  |  |  |

| R <sub>IN</sub>  | Attenuator Input Resistance | 20         | 32  |        | k ohm | Gain = 0dB                                                                                    |  |  |  |  |

| T <sub>HD</sub>  | Total Harmonic Distortion   |            | 0.2 |        | %     | 2Vp-p, 1 kHz,<br>Gain = 0dB                                                                   |  |  |  |  |

| SNR              | Signal to Noise Ratio       |            | 86  |        | dB    | Gain = 0dB<br>BW = 20 to 20 kHz                                                               |  |  |  |  |

| Rmono            | Mono Switch Resistance      | 100        | 200 | 400    | ohms  |                                                                                               |  |  |  |  |

| N <sub>CR</sub>  | Crosstalk - L/R Channel     |            | 78  |        | dB    | $\begin{array}{l} 1 \text{ kHz, } 2 \text{ V}_{P-P} \\ \text{Gain} = 0 \text{db} \end{array}$ |  |  |  |  |

| ΔG               | Analog Output Step          |            | 0.5 |        | dB    | Atten. value<br>127 through 16                                                                |  |  |  |  |

|                  |                             | DIG        | TAL |        |       |                                                                                               |  |  |  |  |

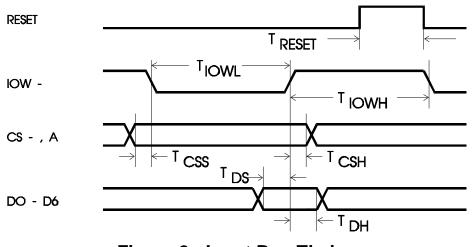

| TRESET           | Reset Pulse Width           | 200        |     |        | ns    |                                                                                               |  |  |  |  |

| TIOWL            | IOW Pulse Width Low         | 80         |     |        | ns    |                                                                                               |  |  |  |  |

| TIOWH            | IOW Pulse Width High        | 120        |     |        | ns    |                                                                                               |  |  |  |  |

| T <sub>CSS</sub> | Chip Select Setup Time      | 25         |     |        | ns    |                                                                                               |  |  |  |  |

| T <sub>CSH</sub> | Chip Select Hold Time       | 25         |     |        | ns    |                                                                                               |  |  |  |  |

| T <sub>DS</sub>  | Data Setup Time             | 25         |     |        | ns    |                                                                                               |  |  |  |  |

| T <sub>DH</sub>  | Data Hold Time              | 25         |     |        | ns    |                                                                                               |  |  |  |  |

Figure 2 - Input Bus Timing

Figure 3 - Block Diagram

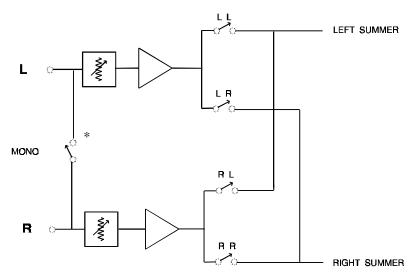

\* The master attenuator pair does not have a mono switch; the connection between the left and right inputs is open.

## Figure 4 - Attenuator Pair Detail

### **Timing Diagram**

## Programming

The **ICS2101** mixer provides two write-only registers (address and data) the host processor can use. Typically the host writes a value to the address register, selecting the appropriate data register for the subsequent data-write operations. For applications such as gradually fading one attenuator, the address register can be written to once at the beginning of the operation. A new data value is needed only when a different attenuator is selected.

## **Address Register**

The address register is used to point to internal registers (attenuator and control).

#### Data Definition

| D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|

| Х  | -  | -  | -  | -  | -  | -  |

|    |    |    |    |    |    |    |

Attenuator Selection

Control Selection

| Attenuator | and Cor | ntrol Reg | ister Se | election |

|------------|---------|-----------|----------|----------|

|------------|---------|-----------|----------|----------|

| D6 | D5 | D4 | D3 | D2 | D1 | D0 | Attenuator and<br>Control Register<br>Definition |

|----|----|----|----|----|----|----|--------------------------------------------------|

| Х  | Х  | Х  | Х  | 0  | 0  | 0  | Control Left                                     |

| Х  | Х  | Х  | Х  | 0  | 0  | 1  | Control Right                                    |

| Х  | Χ  | Χ  | Х  | 0  | 1  | 0  | Attenuator Left                                  |

| Х  | Х  | Х  | Х  | 0  | 1  | 1  | Attenuator Right                                 |

| Х  | Х  | Х  | Χ  | 1  | 0  | Χ  | Pan/Balance                                      |

| Х  | 0  | 0  | 0  | Х  | Х  | Х  | Pair 1                                           |

| Х  | 0  | 0  | 1  | Х  | Х  | Х  | Pair 2                                           |

| Х  | 0  | 1  | 0  | Х  | Х  | Х  | Pair 3                                           |

| Х  | 0  | 1  | 1  | Х  | Х  | Х  | Pair 4                                           |

| Х  | 1  | 0  | 0  | Х  | Х  | Χ  | Pair 5                                           |

| Х  | 1  | 0  | 1  | Х  | Х  | Х  | Master                                           |

### **Attenuation Register**

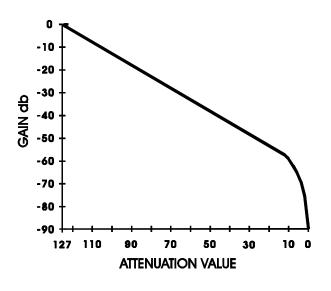

Each attenuator is controlled by a 7-bit value written to the control register. The values of 127 through 16 will increase the attenuation linearly in one-half decibel (dB) increments. Values of 15 through 0 will cause the attenuation to increase at an increasing rate, with a value of 00H corresponding to maximum attenuation. The channel is off when the control register value is 00H and at maximum volume (completely on) with a value of 7FH.

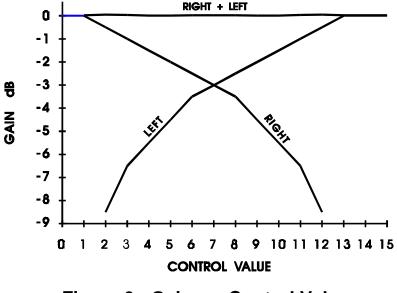

### Figure 5 - Gain vs. Control Value

### **Modes of Operation**

Each attenuator pair may operate in one of three modes:

- Normal mode

- Stereo mode

- Balance/Pan mode

#### Normal Mode

Normal mode is used for applications with mono inputs. In this mode, both internal attenuator (left and right) and control registers (left and right) are utilized. Each may be controlled separately.

#### Stereo Mode

The operation of the attenuator pair in stereo mode is controlled by the left control register. The data written to the left control register is also written to the right control register; therefore, application software need not write to the right control or right attenuation register while operating in this mode. The gain of both channels will be identical in stereo mode. The master attenuator pair does not have a mono switch and cannot be operated in any mode requiring the mono switch to be in the closed (or on) position.

#### Balance/Pan Mode

The operation of the attenuator pair in balance/pan mode is controlled by the left control register. The data written to the left control register is also written to the right control register; therefore, need not write to the right control or right attenuation register while operating in this mode. The balance/pan register controls the gain of the attenuator pair by regulating the balance and the pan position of the output signals. The master attenuator pair does not have a mono switch and cannot be operated in any mode requiring the mono switch to be in the closed (or on) position. The master attenuator pair cannot be used in pan mode.

In the pan/balance mode, two separate registers are used to control the attenuator pair. The attenuation value directed to the left attenuator register is modified by the contents of the pan/balance register, and the appropriate values are then written to the left and right attenuator registers. When the pan/balance register of a channel is modified, the data value has no effect on the attenuator settings until the next value is written to the left attenuator register.

Figure 6 - Gain vs. Control Value

## Modes of Operation -Data Values and Switch Settings

### Right Control Register

| D6 | D5 | D4 | D3 | D2 | D1 | <b>D</b> 0 | LL | LR | RL  | RR  | Mono | Mode of Operation |

|----|----|----|----|----|----|------------|----|----|-----|-----|------|-------------------|

| Х  | Х  | Х  | 0  | 0  | 0  | 0          | Х  | Х  | Off | Off | Off  | Normal            |

| Х  | Х  | Х  | 0  | 0  | 0  | 1          | Х  | Х  | On  | Off | Off  | Normal            |

| Х  | Х  | Х  | 0  | 0  | 1  | 0          | Х  | Х  | Off | On  | Off  | Normal            |

| X  | Х  | Х  | 0  | 0  | 1  | 1          | Х  | Х  | On  | On  | Off  | Normal            |

### Left Control Register

| D6 | D5 | D4 | D3 | D2 | D1 | D0 | LL  | LR  | RL  | RR  | Mono | Mode of Operation           |

|----|----|----|----|----|----|----|-----|-----|-----|-----|------|-----------------------------|

| Х  | Х  | Х  | 0  | 0  | 0  | 0  | Off | Off | Х   | Х   | Off  | Normal                      |

| Х  | Х  | Х  | 0  | 0  | 0  | 1  | On  | Off | Х   | Х   | Off  | Normal                      |

| Х  | Х  | Х  | 0  | 0  | 1  | 0  | Off | On  | Х   | Х   | Off  | Normal                      |

| X  | Х  | Х  | 0  | 0  | 1  | 1  | On  | On  | Х   | Х   | Off  | Normal                      |

| X  | Х  | Х  | 0  | 1  | 0  | 0  | On  | Off | Off | On  | Off  | Stereo - Normal             |

| Х  | Х  | Х  | 0  | 1  | 0  | 1  | Off | On  | On  | Off | Off  | Stereo - Reversed Channels  |

| X  | Х  | Х  | 0  | 1  | 1  | 0  | On  | Off | Off | On  | On   | Mono                        |

| X  | Х  | Х  | 0  | 1  | 1  | 1  | Off | On  | On  | Off | On   | Mono (Reserved)             |

| X  | Х  | Х  | 1  | 0  | 0  | 0  | On  | Off | Off | On  | Off  | Balance - Normal            |

| X  | Х  | Х  | 1  | 0  | 0  | 1  | Off | On  | On  | Off | Off  | Balance - Reversed Channels |

| Х  | Х  | Х  | 1  | 0  | 1  | 0  | On  | Off | Off | On  | On   | Pan - Normal                |

| Х  | Х  | Х  | 1  | 0  | 1  | 1  | Off | On  | On  | Off | On   | Pan - Reversed              |

28-Pin DIP Package

## Ordering Information ICS2101N

Example: