## StrongARM\*\*SA-1100 Microprocessor

**Specification Update**

November 1998

**Notice:** The SA-1100 may contain design defects or errors known as errata. Characterized errata that may cause the SA-1100's behavior to deviate from published specifications are documented in this specification update.

Order Number: 278105-006

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SA-1100 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

\*\*ARM and StrongARM are trademarks of Advanced RISC Machines, Ltd.

| Revision History             | 1  |

|------------------------------|----|

| Preface                      | 2  |

| Summary Table of Changes     | 4  |

| Identification Information   | 7  |

| Related Information          | 8  |

| Errata                       | 9  |

| Specification Changes        | 11 |

| Specification Clarifications | 12 |

| Documentation Changes        | 13 |

# Revision History

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/10/98 | 006     | Under Specification Changes, added new Appendix D, Internal Test.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10/22/98 | 005     | Under Affected Documents/Related Documents, added product discontinuance information.  Under Specification Changes and Document Changes, added product discontinuance information.  Under Markings, added product discontinuance information.  Under Specification Changes, added product discontinuance information.  Under Document Changes, added change to Table 1-1, Table 1-2, Table 8-1, and Section 11.12.4.1.  Under Errata, added errata for slow SIR.       |

| 09/25/98 | 004     | Under Affected Documents/Related Documents, added StrongARM to precede SA-1100 in the titles for the two brief datasheets.                                                                                                                                                                                                                                                                                                                                             |

| 09/18/98 | 003     | Under Identification Information, removed DE-S1100-BA and DE-S1100-BB to show discontinuance.  Under Documentation Changes, removed references to -BA and -BB parts to show discontinuance.  On the title page, StrongARM added to precede SA-1100 in the title.                                                                                                                                                                                                       |

| 08/25/98 | 002     | Under Documentation Changes, changed page, table, and figure #s to show change to Intel format. Added change to Table 12-1, Table 12-2, Table 12-3, Table 13-1, Table 13-2, Figure 14-1 and Section 3.2.6.  Under Identification Information, added DE-S1100-EA, DE-S1100-AB, DE-S1100-BB, DE-S1100-CB, DE-S1100-DB, AND DE-S1100-EB.  Under Affected Documents/Related Documents, removed SA-1100 Data Sheet to show discontinuance.  Under Errata, added two errata. |

| 07/14/98 | 001     | Product line order number sequence change, from 280105-001 to 278105-001.  Under Affected Documents/Related Documents, changed order #s to show change to Intel order #s.                                                                                                                                                                                                                                                                                              |

| 06/15/98 | 001     | This is the new Specification Update document. It contains all identified errata published prior to this date.                                                                                                                                                                                                                                                                                                                                                         |

### **Preface**

As of July, 1996, Intel's Computing Enhancement Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### **Affected Documents/Related Documents**

| Title                                                      | Order      |

|------------------------------------------------------------|------------|

| SA-1100 Microprocessor Technical Reference Manual          | 278088-001 |

| StrongARM SA-1100 Microprocessor for Portable Applications | 278087-002 |

| StrongARM SA-1100 Microprocessor for Embedded Applications | 278092-002 |

#### 08/25/98

Removed reference to the SA-1100 Microprocessor Datasheet (278179-001) as it is no longer in publication.

#### **Nomenclature**

**Errata** are design defects or errors. These may cause the published (component, board, system) behavior to deviate from published specifications. Hardware and software designed to be used with any component, board, and system must consider all errata documented.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

Note:

Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

## Summary Table of Changes

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the SA-1100 product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### **Codes Used in Summary Table**

#### **Stepping**

X: Errata exists in the stepping indicated. Specification Change or

Clarification that applies to this stepping.

(No mark)

or (Blank box): This erratum is fixed in listed stepping or specification change does not

apply to listed stepping.

**Page**

(Page): Page location of item in this document.

**Status**

Doc: Document change or update will be implemented.

Fix: This erratum is intended to be fixed in a future step of the component.

Fixed: This erratum has been previously fixed.

NoFix: There are no plans to fix this erratum.

Eval: Plans to fix this erratum are under evaluation.

Row

Change bar to left of table row indicates this erratum is either new or

modified from the previous version of the document.

### **Errata**

| No. | Steppings |   | Page Status |      | ERRATA |                                                                              |

|-----|-----------|---|-------------|------|--------|------------------------------------------------------------------------------|

| NO. | E         | # | #           | raye | Status | ERRAIA                                                                       |

| 1   | Х         |   |             | 9    | Fix    | Possible Missed RTC Alarm                                                    |

| 2   | Х         |   |             | 9    | Fix    | Transmit Behavior Causing Generation of Five Consecutive Ones at End of CRC  |

| 3   | Х         |   |             | 9    | Fix    | Restriction on Clearing LCD AC Bias Count (ABC) Status Bit                   |

| 4   | Х         |   |             | 10   | Fix    | Receiver to Receive Data Frequency in Slow Infrared Mode (SIR)               |

| 5   | Х         |   |             | 10   | Fix    | Incorrect Transmit Pulse Width in Low-Power Mode in Slow Infrared Mode (SIR) |

| 6   | Х         |   |             | 10   | Fix    | Possible Corrupted Start Bit in Slow Infrared Mode (SIR)                     |

## **Specification Changes**

| No.  | Steppings |   | Page        | Status | SPECIFICATION CHANGES     |

|------|-----------|---|-------------|--------|---------------------------|

| 140. | E         | # | raye Status |        | SI EGII IGATION GITANGES  |

| 1    | Х         |   | 11          | Eval   | USB Feature               |

| 2    | Х         |   | 11          | Doc    | Product Discontinuance    |

| 3    | Х         |   | 11          | Doc    | Appendix D, Internal Test |

## **Specification Clarifications**

| No.  | Steppings |   | 11 0 |             | Page                              | Status                                               | SPECIFICATION CLARIFICATIONS |

|------|-----------|---|------|-------------|-----------------------------------|------------------------------------------------------|------------------------------|

| 140. | #         | # | #    | Page Status | SI ESII ISATISNI SEANII ISATISNIS |                                                      |                              |

|      |           |   |      |             |                                   | None for this revision of this specification update. |                              |

## **Documentation Changes**

| No. | Document Revision | Page                                                                                  | Status DOCUMENTATION CHANGES                               |                                                                                 |

|-----|-------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1   | 278088-001        | 14                                                                                    | 14 Doc DC Maximum Ratings: Table 12-1                      |                                                                                 |

| 2   | 278088-001        | 14                                                                                    | 14 Doc DC Operating Conditions: Table 12-2                 |                                                                                 |

| 3   | 278088-001        | 14 Doc Power Supply Voltages and Currents Table for TQI and mBGA Packages: Table 12-3 |                                                            | Power Supply Voltages and Currents Table for TQFP and mBGA Packages: Table 12-3 |

| 4   | 278088-001        | 15                                                                                    | 15 Doc Output Derating Table: Table 13-1                   |                                                                                 |

| 5   | 278088-001        | 15                                                                                    | 15 Doc AC Timing Table: Table 13-2                         |                                                                                 |

| 6   | 278088-001        | 15                                                                                    | Doc SA-1100 208-Pin LQFP Mechanical Drawing: Figur<br>14-1 |                                                                                 |

| 7   | 278088-001        | 16                                                                                    | Doc                                                        | Interrupt Latencies: Section 3.2.6                                              |

## **Documentation Changes**

| No. | Document Revision | Page                                                   | Status DOCUMENTATION CHANGES |                                           |

|-----|-------------------|--------------------------------------------------------|------------------------------|-------------------------------------------|

| 8   | 278088-001        | 16 Doc Product Discontinuance: Table 1-1 and Table 1-2 |                              |                                           |

| 9   | 278088-001        | 16 Doc Core Clock Configurations: Table 8-1            |                              |                                           |

| 10  | 278088-001        | 16                                                     | Doc                          | MCCR1 Register Address: Section 11.12.4.1 |

## Identification Information

### **Markings**

DE-S1100-AA, DE-S1100-CA, DE-S1100-DA, DE-S1100-EA, DE-S1100-AB, DE-S1100-CB, DE-S1100-DB, and DE-S1100-EB.

This document contains errata for the SA-1100 Microprocessor. The SA-1100 device revision that is affected by this errata can be identified as order numbers DE-S1100-AA, DE-S1100-CA, DE-S1100-DA, DE-S1100-EA, DE-S1100-AB, DE-S1100-CB, DE-S1100-DB, and DE-S1100-EB.

| Markings    | Speed (MHz) | Voltage (V) | Package |

|-------------|-------------|-------------|---------|

| DE-S1100-AA | 133         | 1.5         | TQFP    |

| DE-S1100-CA | 160         | 2.0         | TQFP    |

| DE-S1100-DA | 220         | 2.0         | TQFP    |

| DE-S1100-EA | 190         | 1.5         | TQFP    |

| DE-S1100-AB | 133         | 1.5         | mBGA    |

| DE-S1100-CB | 160         | 2.0         | mBGA    |

| DE-S1100-DB | 220         | 2.0         | mBGA    |

| DE-S1100-EB | 190         | 1.5         | mBGA    |

09/16/98

Removed markings DE-S1100-BA and DE-S1100-BB to show product discontinuance.

## Related Information

As of May 17, 1998, Digital Equipment Corporation's StrongARM, PCI Bridge, and Networking component businesses, along with the chip fabrication facility in Hudson, Massachusetts, were acquired by Intel Corporation. As a result of this transaction, certain references to web sites, telephone numbers, and fax numbers have changed in the documentation. Updates to this information are planned for the next version of this manual. Copies of documents that have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling:

**1-800-332-2717** or by visiting Intel's website for developers at:

http://developer.intel.com

The Intel Massachusetts Customer Technology Center services your StrongARM Product, Bridge Product, and Network Product technical inquiries. Please use the following information lines for support:

| For Documentation and General Information  | For Technical Support                          |

|--------------------------------------------|------------------------------------------------|

| Intel Massachusetts Information Line       | Intel Massachusetts Customer Technology Center |

| United States: 1–800–332–2717              | Phone (U.S. and international): 1-978-568-7474 |

| Outside United States: 1–303–675–2148      | Fax: 1-978-568-6698                            |

| Electronic mail address: techdoc@intel.com | Electronic mail address: techsup@intel.com     |

### Errata

1. Possible Missed RTC Alarm

**Problem:** If an RTC alarm occurs just as the SA-1100 is entering or leaving sleep mode, the alarm status bit

(AL, bit 0 in RTSR) could fail to be set.

Workaround: A software workaround intended to provide a way to avoid missing an RTC alarm is available. If

the RTC alarm is set:

1. Read the RTC Timer (RCNR) and Alarm register (RTAR) before entering sleep mode via software. The RTAR must be greater than or equal to RCNR + 2 in order to ensure that an RTC alarm is not missed while entering sleep mode.

2. Read the RTC Timer (RCNR) and Alarm register (RTAR) after a sleep wakeup to determine if an alarm occurred.

**Status:** Fix. Refer to Summary Table of Changes to determine the affected stepping(s).

## 2. Transmit Behavior Causing Generation of Five Consecutive Ones at End of CRC

**Problem:** If the data within a packet transmitted by the SDLC transmitter causes the last five bits within the

CRC to be all ones, the SDLC does not insert a zero into the serial data being output.

For example, the SDLC transmits the following:

start addr cntl data CRC...011111 01111110

when it should transmit:

start | addr | cntl | data | CRC...0111110 | 01111110 |

The SDLC receiver does not strip a zero after five ones are encountered at the end of the receive packet CRC. However, the SDLC receiver correctly detects a packet either with or without a

stuffed zero at the end.

Workaround: None. Off-chip receivers can signal errors when detecting data that causes five consecutive ones to

be generated at the end of the CRC.

**Status:** Fix. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 3. Restriction on Clearing LCD AC Bias Count (ABC) Status Bit

**Problem:** If the user programs the AC Bias Pin Transition Per Interrupt (API) bit-field to a nonzero value and

the AC Bias Count (ABC) status bit is set, writing a one to the bit does not clear it. Only a reset of

the SA-1100 can clear the ABC.

**Workaround:** The API should be programmed to all zeros.

**Status:** Fix. Refer to Summary Table of Changes to determine the affected stepping(s).

4. Receiver to Receive Data Frequency in Slow Infrared Mode (SIR)

**Problem:** When serial port 2 (SP2) is configured for operation in SIR mode and the remote transmitter

frequency is higher by 0.13 % or more than the SP2 Sir receiver clock supplied by the 3.6864-MHz PLL and bit rate generator, some percentage of the received data is corrupted by the addition of

spurious bit.

Note: According to IrDA Serial Infrared Physical Layer Link Specification V 1.2, the allowable rate

deviation tolerance is  $\pm$  0.87% when operating in SIR mode.

Workaround: None. Off-chip IrDA receivers can be used to format and synchronize the incoming data so that it

can be input to the on-chip UART via SP2.

**Status:** Fix. Refer to Summary Table of Changes to determine the affected stepping(s).

5. Incorrect Transmit Pulse Width in Low-Power Mode in Slow Infrared Mode

(SIR)

**Problem:** When serial port 2 (SP2) is configured for operation in SIR mode and the UART control register 4

(UTCR4) LPB bit is set, the transmitted pulse is equal to 3/8 of a bit time.

Note: According to IrDA Serial Infrared Physical Layer Link Specification V 1.2, the nominal minimum

pulse width is 1.63 µs regardless of the signaling rate when operating in low-power SIR mode.

**Workaround:** Do not use low-power (LPM) mode in SIR. Always set LPM of UTCR4 to zero.

**Status:** Fix. Refer to Summary Table of Changes to determine the affected stepping(s).

6. Possible Corrupted Start Bit in Slow Infrared Mode (SIR)

**Problem:** When serial port 2 (SP2) is configured for operation in SIR mode, there is the possibility that the

loading of the Transmit FIFO while the IrDA transmitter is active can cause the transmitted start bit to be corrupted. If the problem occurs, the start bit will go active 5/16 of a bit-time too early and

will remain active for 8/16 of a bit-time, instead of the required time of 3/16 of a bit-time.

Workaround: None. Off-chip IrDA transmitters can be used to format the outgoing data from the on-chip UART

via SP2.

**Status:** Fix. Refer to Summary Table of Changes to determine the affected stepping(s).

## Specification Changes

#### 1. USB Feature

The USB feature is not available in this release of the product.

#### 2. Product Discontinuance

Effective October 16, 1998, Intel will no longer offer a 200 MHz version of the SA-1100 RISC microprocessor due to a product line consolidation. It is replaced by a new version of the same device offered at 190 MHz @ 1.5 V. This device can be ordered in both a TQFP and mBGA package.

#### 3. Appendix D, Internal Test

New Appendix D added for Internal Test.

The Test Unit contains a register that enables certain test modes. Some of these test modes are reserved for manufacturing test and should not be invoked by an end user.

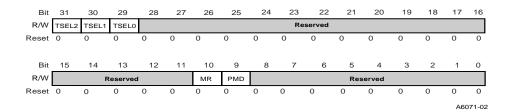

### Test Unit Control Register (TUCR)

The Test Unit Control Register (TUCR) contains control bits that put the SA-1100 in various test modes. It is recommended that the operating system write protect these registers under normal conditions to prevent them from being inadvertently written. The following figure shows the format of this register. At reset reserved bits are zero. Writing reserved bits to one can lead to UNPREDICTABLE results.

| Bit | Name     | Description                                                                                                                                                                                     |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05  | Reserved | _                                                                                                                                                                                               |

| 6   | Reserved | _                                                                                                                                                                                               |

| 7   | Reserved |                                                                                                                                                                                                 |

| 8   | Reserved | _                                                                                                                                                                                               |

| 9   | PMD      | Power management disable.  When PMD is set, sleep mode is disabled and the SA-1100 ignores the ForceSleep bit, as well as the BATT_FAULT and VDD_Fault pins. This bit is cleared on hard reset. |

| Bit  | Name     | Description                                                                                                                                                                                                                                                          |                                 |                                 |                                                                                                                                                                                    |  |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10   | MR       | Memory request mode. Controls two GPIO pins used for external arbitration and for the memory bus.                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

|      |          | 0 – GP[21] and GP[22] are not used for an alternate function. 1 – GP[21] and GP[22] are reserved for use as MBREQ and MBGNT.                                                                                                                                         |                                 |                                 |                                                                                                                                                                                    |  |

| 1119 | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 20   | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 21   | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 22   | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 23   | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 24   | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 25   | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 26   | Reserved | _                                                                                                                                                                                                                                                                    |                                 |                                 |                                                                                                                                                                                    |  |

| 2728 | Reserved | <u> </u>                                                                                                                                                                                                                                                             |                                 |                                 |                                                                                                                                                                                    |  |

| 2931 | TSEL2-0  | Test selects. Routes internal signals out onto GPIO<27> for observing internal clock signals. To observe these clocks, set bit 27 to one in the GAFR and GPDI registers and set the TSEL bits to the following settings to select which clock is driven onto GP<27>: |                                 |                                 |                                                                                                                                                                                    |  |

|      |          | TSEL2                                                                                                                                                                                                                                                                | TSEL1                           | TSEL0                           | GP<27>(alternate function)                                                                                                                                                         |  |

|      |          | 0<br>0<br>0<br>0<br>1<br>1<br>1                                                                                                                                                                                                                                      | 0<br>0<br>1<br>1<br>0<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | 32-kHz oscillator 3.6864-MHz oscillator VDD ring oscillator/16 96-MHz PLL/4 32-kHz oscillator (also enable rclk on GP<26> 3.6864-MHz oscillator Main PLL/16 VDDL ring oscillator/4 |  |

# Specification Clarifications

None for this revision of this specification update.

## **Documentation Changes**

#### 1. DC Maximum Ratings: Table 12-1

V<sub>DD</sub>

Maximum value changed to Vss + 2.1 V for all variants.

•  $V_{IP}$  (\*XTAL)

New table entry added to cover voltage limitations for \*XTAL pins. Minimum value is 0 V and maximum value is 1 V.

#### 2. DC Operating Conditions: Table 12-2

V<sub>IHC</sub>

Not tested at this time.

V<sub>ILC</sub>

Not tested at this time.

T<sub>A</sub>

Minimum value changed to 0° C and maximum value changed to 70° C.

C<sub>IN</sub>

Parameter guaranteed by design.

## 3. Power Supply Voltages and Currents Table for TQFP and mBGA Packages: Table 12-3

- CA and DA parameters included.

- EA parameters added.

- AB, CB, DB and EB parameters added.

- Information added for the following parameters: typical run mode power, maximum idle power, and typical sleep current.

- Values for idle power and sleep current are specified at room temperature.

- Values for power dissipation, particularly in idle mode, are strongly dependent on the details of the system design.

Table 12-3. SA-1100 Power Supply Voltages and Currents with TQFP Package

| SA-1100                                          |        |        |        |        |     |  |  |

|--------------------------------------------------|--------|--------|--------|--------|-----|--|--|

| Parameter                                        |        | Units  |        |        |     |  |  |

|                                                  | AA/AB* | CA/CB* | DA/DB* | EA/EB* |     |  |  |

| Maximum operating frequency                      | 133    | 160    | 220    | 190    | MHz |  |  |

| Maximum run mode power (total VDD + VDDX)        | 400    | 1100   | 1100   | 500    | mW  |  |  |

| Typical run mode power (total VDD + VDDX)        | 230    | 430    | 550    | 330    | mW  |  |  |

| Maximum idle mode power** (total VDD + VDDX)     | 55     | n/a    | n/a    | 85     | mW  |  |  |

| Typical idle mode power** (total VDD + VDDX)     | 50     | n/a    | n/a    | 65     | mW  |  |  |

| Maximum sleep mode current ** (total VDD + VDDX) | 50     | n/a    | n/a    | 50     | uA  |  |  |

| Typical sleep mode current ** (total VDD + VDDX) | 25     | n/a    | n/a    | 30     | uA  |  |  |

| VDD                                              |        |        |        |        |     |  |  |

| Minimum internal power supply voltage            | 1.42   | 1.90   | 1.90   | 1.42   | V   |  |  |

| Nominal internal power supply voltage            | 1.50   | 2.00   | 2.00   | 1.50   | V   |  |  |

| Maximum internal power supply voltage            | 1.58   | 2.10   | 2.10   | 1.58   | V   |  |  |

| VDDX                                             |        |        |        |        |     |  |  |

| Minimum external power supply voltage            | 3.00   | 3.00   | 3.00   | 3.00   | V   |  |  |

| Nominal external power supply voltage            | 3.30   | 3.30   | 3.30   | 3.30   | V   |  |  |

| Maximum external power supply voltage            | 3.60   | 3.60   | 3.60   | 3.60   | V   |  |  |

$<sup>^{\</sup>ast}$  AA, CA, DA and EA refer to TQFP package. AB, CB, DB and EB refer to mBGA package.

#### 4. Output Derating Table: Table 13-1

- All parameters guaranteed by design.

- Output derating (VDD = 2.0 V rising edge) changed to 0.08ns/pF.

- Output derating (VDD = 2.0 V falling edge) changed to 0.072 ns/pF.

#### 5. AC Timing Table: Table 13-2

• All parameters guaranteed by design. Data needs to be added for CA and DA parts.

#### 6. SA-1100 208-Pin LQFP Mechanical Drawing: Figure 14-1

• Typical pin spacing changed from .60 mm to .50 mm.

<sup>\*\*</sup> Room temperature specification.

#### 7. Interrupt Latencies: Section 3.2.6

Section 3.2.6 Interrupt Latencies replaced with Section 3.2.6 Interrupt Latencies and Enable Timing containing the following information: "The ability to recognize an IRQ or FIQ interrupt is, in part, determined by the I and F bits of the CPSR. To ensure that a pending interrupt is taken, an interrupt-enabling write to CPSR (msr instruction) must be separated from an interrupt-disabling write to the CPSR by at least two instructions."

#### 8. Product Discontinuance: Table 1-1 and Table 1-2

Removed references to DE-S1100-BA and DE-S1100-BB to show product discontinuance. The new performance, power and package information described in Table 1-1 and Table 1-2 can be found in Table 12-3 (shown on p.13 of this specification).

#### 9. Core Clock Configurations: Table 8-1

New table entry added for 220 MHz clock.

| CCF[4:0]      | Core Clock Frequency in MHz<br>3.6864-MHz Crystal Oscillator | Core Clock Frequency in MHz<br>3.5795-MHz Crystal Oscillator |

|---------------|--------------------------------------------------------------|--------------------------------------------------------------|

| 01011         | 221.2                                                        | 214.8                                                        |

| 01100 — 11111 | Not supported.                                               | _                                                            |

#### 10. MCCR1 Register Address: Section 11.12.4.1

The MCP control register (MCCR1) address changed from 0h 8006 0030 to 0h 9006 0030.