PowerPC<sup>TM</sup> Microprocessor Common Hardware Reference Platform: I/O Device Reference

#### LICENSE INFORMATION

To the extent that Apple Computer, Inc., International Business Machines Corporation, and Motorola, Inc. (referred to as "the creators") own licensable copyrights in the *PowerPC Microprocessor Common Hardware Reference Plat-form: I/O Device Reference* (including accompanying source code samples), the creators grant you a copyright license to copy and distribute portions of this document (including accompanying source code samples) in any form, without payment to the creators, for the purpose of developing original documents, code, or equipment (except integrated circuit processors) which conform to the requirements in this document and for the purpose of using, reproducing, marketing, and distributing such code or equipment. This authorization applies to the content of this specification only and not to the referenced material. This authorization does not give you the right to copy and distribute this document in its entirety.

In consideration you agree to include for each reproduction of any portion of these documents or any derivative works the copyright notice as displayed below.

You are responsible for payment of any taxes, including personal property taxes, resulting from this authorization. If you fail to comply with the above terms, your authorization terminates.

The creators and others may have patents or pending patent applications, or other intellectual property rights covering the subject matter described herein. This document neither grants or implies a license or immunity under any of the creators or third party patents, patent applications or other intellectual property rights other than as expressly provided in the above copyright license. The creators assume no responsibility for any infringement of third party rights resulting from your use of the subject matter disclosed in, or from the manufacturing, use, lease, or sale of products described in, this document.

Licenses under utility patents of IBM® in the field of information handling systems are available on reasonable and non-discriminatory terms. IBM does not grant licenses to its appearance design patents. Direct your licensing inquiries in writing to the IBM Director of Licensing, International Business Machines Corporation, 500 Columbus Avenue, Thornwood, NY 10594.

Licenses under utility patents of Apple Computer, Inc., that are necessary to implement the specification set forth in this document are available on reasonable and non-discriminatory terms. Apple Computer, Inc. does not grant licenses to its appearance design patents. Direct your licensing inquires in writing to Mac OS Licensing Department, Apple Computer, Inc., 1 Infinite Loop, MS 38-LG, Cupertino, CA 95014.

© Copyright Apple Computer, Inc., International Business Machines Corporation, Motorola, Inc. 1996. All rights reserved.

Note to U.S. Government Users—Documentation related to restricted rights—Use, duplication, or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

#### NOTICES

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law. In such countries, the minimum country warranties will apply.

THE CREATORS PROVIDE THIS DOCUMENT (INCLUDING ACCOMPANYING SOURCE CODE EXAM-PLES) "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICU-LAR PURPOSE. THE DISCLAIMER OF WARRANTY APPLIES NOT ONLY TO THE DOCUMENT (INCLUD-ING ACCOMPANYING SOURCE CODE EXAMPLES) BUT ALSO TO ANY COMBINATIONS, INCORPORATIONS, OR OTHER USES OF THE DOCUMENT (INCLUDING ACCOMPANYING SOURCE CODE EXAMPLES) UPON WHICH A CLAIM COULD BE BASED.

Some states do not allow disclaimers of express or implied warranties in certain transactions; therefore, this statement may not apply to you.

These materials could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the document. The creators may make improvements and/or changes in the product(s) and/or the program(s) described in, or accompanying, this document at any time.

It is possible that this document may contain reference to, or information about, products (machines and programs), programming, or services of the creators that are not announced in your country. Such reference or information must not be construed to mean that the creators intend to announce such products, programming, or services in your country.

Requests for copies of this document or for technical information about products described herein should be directed to the creators. Refer to "Obtaining Additional Information" on page 263 for a description of information available and telephone numbers.

Version 1.0 (May 1996)

#### TRADEMARKS AND SERVICE MARKS

Trademarks or service marks in the United States or other countries are denoted by a registered symbol (<sup>®</sup>) or a trademark symbol(<sup>TM</sup>) on their first occurrence in this document. See "Trademark Information" on page 259 for a complete listing of all referenced trademarks and the companies that own them.

# РоwerPC<sup>TM</sup> Microprocessor Common Hardware Reference Platform: I/O Device Reference (Draft Version 0.9)

Developed by Apple Computer, Inc., International Business Machines Corporation, and Motorola, Inc.

# Contents

| About this Document                                 | xxii  |

|-----------------------------------------------------|-------|

| Goals of this Specification                         | xxii  |

| Audience for this Document                          | xxiv  |

| Organization of this Document                       | xxiv  |

| Suggested Reading                                   | XXV   |

| Conventions Used in this Document                   | XXV   |

| Acknowledgments                                     | xxvii |

| Comments on this Document                           | xxvii |

| Chapter 1 General Requirements and Information      | 1     |

| 1.1 General Requirements                            | 1     |

| 1.2 Credit for Material                             | 1     |

| 1.2.1 From National Semiconductor Corporation       | 1     |

| Chapter 2 ISA DMA Controller                        | 3     |

| 2.1 Minimum System Requirements                     | 3     |

| 2.2 References                                      | 4     |

| 2.3 ISA DMA Controller Open Firmware Properties     | 4     |

| 2.4 DMA Channel Registers                           | g     |

| 2.4.1 Current Address Register 0 (CA0)              | g     |

| 2.4.2 Current Address Registers (CA1-CA7)           | 10    |

| 2.4.3 Base Address Register 0 (BA0)                 | 10    |

| 2.4.4 Base Address Registers 1-7 (BA1-BA7)          | 10    |

| 2.4.5 Current Count Register 0 (CC0)                | 11    |

| 2.4.6 Current Count Registers 1-7 (CC1-CC7)         | 11    |

| 2.4.7 Base Count Register 0 (BC0)                   | 12    |

| 2.4.8 Base Count Registers 1-7 (BC1-BC7)            | 12    |

| 2.4.9 Current Low Page Register 0 (CLOP0)           | 12    |

| 2.4.10 Current Low Page Register 1-7 (CLOP1-CLOP7)  | 13    |

| 2.4.11 Base Low Page Register 0 (BLOP0)             | 13    |

| 2.4.12 Base Low Page Register 1-7 (BLOP1-BLOP7)     | 13    |

| 2.4.13 Current High Page Register 0 (CHIP0)         | 13    |

| 2.4.14 Current High Page Register 1-7 (CHIP1-CHIP7) | 14    |

| 2.4.15 Base High Page Register 0 (BHIP0)            | 14    |

| 2.4.16 Base High Page Register 1-7 (BHIP1-BHIP7)    | 14    |

| 2.5 DMA Controller Registers                        | 15    |

| 2.5.1 DMA 1 Command Register (DCOM1)                | 15    |

| 2.5.2 DMA 2 Command Register (DCOM2)                | 16    |

| 2.5.3 DMA 1 Channel Mode Register (DCM1)            | 16    |

| 2.5.4 DMA 2 Channel Mode Register (DCM2)                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2.5.5 DMA 1 Extended Mode Register (DCEM1)                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                 |

| 2.5.6 DMA 2 Extended Mode Register (DCEM2)                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                 |

| 2.5.7 DMA 1 Request Register (DR1)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19                                                 |

| 2.5.8 DMA 2 Request Register (DR2)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20                                                 |

| 2.5.9 DMA 1 Write Single Bit Mask Register (WSM1)                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                 |

| 2.5.10 DMA 2 Write Single Bit Mask Register (WSM2)                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |

| 2.5.11 DMA 1 Write All Mask Bits Register (WAM1)                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                 |

| 2.5.12 DMA 2 Write All Mask Bits Register (WAM2)                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                 |

| 2.5.13 DMA 1 Status Register (DS1)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                 |

| 2.5.14 DMA 2 Status Register (DS2)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                 |

| 2.5.15 DMA 1 Clear Byte Pointer Register (CBP1)                                                                                                                                                                                                                                                                                                                                                                                                                        | 23                                                 |

| 2.5.16 DMA 2 Clear Byte Pointer Register (CBP2)                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                 |

| 2.5.17 DMA 1 Master Clear Register (DMC1)                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                 |

| 2.5.18 DMA 2 Master Clear Register (DMC2)                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                 |

| 2.5.19 DMA 1 Clear Mask Register (DCLM1)                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                 |

| 2.5.20 DMA 2 Clear Mask Register (DCLM2)                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                 |

| 2.6 Scatter/Gather Registers                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                 |

| 2.6.1 The Scatter/Gather Descriptor                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                 |

| 2.6.2 Scatter/Gather Interrupt Status Register (SGIS)                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| 2.6.3 Scatter/Gather Command Register 0 (SGC0)                                                                                                                                                                                                                                                                                                                                                                                                                         | 27                                                 |

| 2.6.4 Scatter/Gather Command Registers 1-7 (SGC2-SGC7)                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                 |

| 2.6.5 Scatter/Gather Status Register 0 (SGS0)                                                                                                                                                                                                                                                                                                                                                                                                                          | 28                                                 |

| 2.6.6 Scatter/Gather Status Register 1-7 (SGS1-SGS7)                                                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                 |

| 2.6.7 Scatter/Gather Descriptor Table Pointer Register 0 (SGPTR0)                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                 |

| 2.6.8 Scatter/Gather Descriptor Table Pointer Registers 1-7 (SGPTR1-SGPTR7)                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                 |

| 2.7 Support for ISA Bus masters                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| Chapter 3 Floppy Disk Controller                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                 |

| 3.1 General Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| 3.2 Floppy Disk/Tape Media Supported                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                                                 |

| 3.3 Floppy Disk Controller Open Firmware Properties                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                                                 |

| 3.4 Diskette Drive Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                | 33                                                 |

| 3.4.1 Status Register A (SRA)                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                 |

| 3.4.2 Status Register B (SRB)                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                 |

| 3.4.3 Digital Output Register (DOR)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35                                                 |

| 3.4.4 Tape Drive Register (TDR)                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                 |

| 3.4.5 Main Status Register (MSR)                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                                 |

| 3.4.6 Data Rate Select Register (DRS)                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                 |

| 3.4.7 Data Register (FIFO)                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                 |

| 3.4.8 Digital Input Register (DIR)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                 |

| 3.4.9 Configuration Control Register (CCR)                                                                                                                                                                                                                                                                                                                                                                                                                             | 41                                                 |

| 3.4.10 Autoeject Register (AEJ)                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                                                 |

| 3.5 Floppy Drive Controller Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| 3.5.1 Controller Commands                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                                 |

| 3.5.2 Command Status Registers Provided During Result Phase                                                                                                                                                                                                                                                                                                                                                                                                            | 56                                                 |

| 3.6 Media Sense                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                 |

| 3.7 Floppy Drive Signal Connector Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                       | 59<br>59                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| 3.7 Floppy Drive Signal Connector Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                                                 |

| <ul><li>3.7 Floppy Drive Signal Connector Pin Assignment</li><li>3.8 References</li></ul>                                                                                                                                                                                                                                                                                                                                                                              | 59<br>60                                           |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> </ul>                                                                                                                                                                                                                                                                                                                            | 59<br>60<br>61                                     |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> </ul>                                                                                                                                                                                                                                                                             | 59<br>60<br>61<br>61                               |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> </ul>                                                                                                                                                                                                                                     | 59<br>60<br>61<br>61<br>63                         |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> <li>4.3 Modes of Operation</li> </ul>                                                                                                                                                                                                     | 59<br>60<br>61<br>61<br>63<br>64                   |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> <li>4.3 Modes of Operation <ul> <li>4.3.1 Fully-Nested Mode</li> </ul> </li> </ul>                                                                                                                                                        | 59<br>60<br>61<br>61<br>63<br>64<br>65             |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> <li>4.3 Modes of Operation <ul> <li>4.3.1 Fully-Nested Mode</li> <li>4.3.2 Special Fully-Nested Mode</li> </ul> </li> </ul>                                                                                                               | 59<br>60<br>61<br>61<br>63<br>64<br>65<br>65       |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> <li>4.3 Modes of Operation <ul> <li>4.3.1 Fully-Nested Mode</li> <li>4.3.2 Special Fully-Nested Mode</li> <li>4.3.3 Automatic Rotation Mode</li> </ul> </li> </ul>                                                                        | 59<br>60<br>61<br>61<br>63<br>64<br>65<br>65<br>66 |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> <li>4.3 Modes of Operation <ul> <li>4.3.1 Fully-Nested Mode</li> <li>4.3.2 Special Fully-Nested Mode</li> <li>4.3.3 Automatic Rotation Mode</li> <li>4.3.4 Specific Rotation Mode</li> </ul> </li> </ul>                                  | 59<br>60<br>61<br>63<br>64<br>65<br>65<br>66<br>66 |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> <li>4.3 Modes of Operation <ul> <li>4.3.1 Fully-Nested Mode</li> <li>4.3.2 Special Fully-Nested Mode</li> <li>4.3.3 Automatic Rotation Mode</li> <li>4.3.4 Specific Rotation Mode</li> <li>4.3.5 Special Mask Mode</li> </ul> </li> </ul> | 59<br>60<br>61<br>61<br>63<br>64<br>65<br>65<br>66 |

| <ul> <li>3.7 Floppy Drive Signal Connector Pin Assignment</li> <li>3.8 References</li> <li>Chapter 4 Legacy Interrupt Controller</li> <li>4.1 Overview and General Requirements</li> <li>4.2 Open Firmware Requirements</li> <li>4.3 Modes of Operation <ul> <li>4.3.1 Fully-Nested Mode</li> <li>4.3.2 Special Fully-Nested Mode</li> <li>4.3.3 Automatic Rotation Mode</li> <li>4.3.4 Specific Rotation Mode</li> </ul> </li> </ul>                                  | 59<br>60<br>61<br>63<br>64<br>65<br>65<br>66<br>66 |

#### Contents

| 4.4 Programming the Interrupt Controller                          | 67  |

|-------------------------------------------------------------------|-----|

| 4.4.1 Initialization Command Word Registers                       | 67  |

| 4.4.2 Operation Command Word Registers                            | 70  |

| 4.4.3 Interrupt Request Register (IRR)                            | 74  |

| 4.4.4 In-Service Register (ISR)                                   | 74  |

|                                                                   | 74  |

| 4.4.5 Edge/Level Interrupt Control Registers (ELI)                |     |

| 4.5 References                                                    | 77  |

| Chapter 5 Parallel Port Controller                                | 79  |

| 5.1 General Requirements                                          | 80  |

| 5.2 Open Firmware Requirements                                    | 82  |

| 5.3 Parallel Port Register Definitions                            | 83  |

| 5.3.1 Registers Used in Multiple Modes                            | 84  |

| 5.3.2 Registers Used Only in EPP Mode                             | 87  |

| 5.3.3 Registers Used Only in ECP Mode                             | 89  |

| 5.3.4 Registers Used Only in the Parallel Port FIFO Mode          | 91  |

| 5.3.5 Registers Used Only in the Test FIFO Mode                   | 91  |

| 5.4 References                                                    | 92  |

| 3.4 Neleiences                                                    | 92  |

| Chapter 6 UART Controller                                         | 93  |

| 6.1 CHRP Requirements                                             | 93  |

| 6.2 UART Controller Open Firmware Requirements                    | 93  |

| 6.3 UART Registers                                                | 94  |

| 6.3.1 Transmitter Data Register (TDR)                             | 95  |

| 6.3.2 Receiver Data Register (RDR)                                | 95  |

| 6.3.3 Interrupt Enable Register (IER)                             | 95  |

| 6.3.4 FIFO Control Register (FCR)                                 | 96  |

| 6.3.5 Interrupt Identification Register (IIR)                     | 97  |

| 6.3.6 Line Control Register (LCR)                                 | 98  |

| 6.3.7 Modem Control Register (MCR)                                | 100 |

| 6.3.8 Line Status Register (LSR)                                  | 100 |

| 6.3.9 Modem Status Register (MSR)                                 | 101 |

| 6.3.10 Scratch Register (SCR)                                     | 102 |

| 6.3.11 Baud Rate Divisor Register (DLL)                           | 102 |

| 6.3.12 Baud Rate Divisor Register (DLH)                           | 102 |

| 6.4 References                                                    | 103 |

|                                                                   |     |

| Chapter 7 ISA Keyboard/Mouse Controller                           | 105 |

| 7.1 Overview and General Requirements                             | 105 |

| 7.2 Keyboard/Mouse Controller Register Table                      | 106 |

| 7.3 Keyboard Controller Registers                                 | 106 |

| 7.3.1 Output Register (OUT)                                       | 107 |

| 7.3.2 Input Register (IN)                                         | 108 |

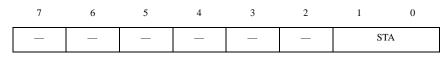

| 7.3.3 Status Register (STA)                                       | 108 |

| 7.3.4 Control Register (CTL)                                      | 109 |

| 7.4 Programming Devices Attached to the Keyboard/Mouse Controller | 111 |

| 7.5 References                                                    | 111 |

| Chanter 9 Audio                                                   | 110 |

| Chapter 8 Audio                                                   | 113 |

| 8.1 Overview                                                      | 113 |

| Chapter 9 ESCC                                                    | 115 |

| 9.1 Overview and General Requirements                             | 115 |

| 9.2 ESCC Controller Open Firmware Properties                      | 116 |

| 9.3 Legacy ESCC Controller Open Firmware Properties               | 117 |

| 9.4 Child Nodes for ESCC Open Firmware Properties                 | 118 |

| 9.5 Child Nodes for ESCC-Legacy Open Firmware Properties          | 119 |

| 9.6 LocalTalk Support                                             | 119 |

| 9.7 ESCC Channel Specific Registers                               | 119 |

|                                                                   | 110 |

ix

| <ul> <li>9.7.1 Command Register</li> <li>9.7.2 Data Register</li> <li>9.7.3 Enhancement Register</li> <li>9.8 ESCC Shared Registers</li> <li>9.8.1 SCC Recovery Count Register</li> <li>9.8.2 LTPC Start A</li> <li>9.8.3 LTPC Start B</li> </ul>                                                                                                                                                                                                                                                                                                                   | 120<br>120<br>120<br>121<br>121<br>122<br>122                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 9.8.4 LTPC Detect AB Register<br>9.8.5 Timer Register<br>9.8.6 Special Character 1 Register<br>9.8.7 Special Character 2 Register<br>9.8.8 Special Character 3 Register                                                                                                                                                                                                                                                                                                                                                                                             | 123<br>123<br>124<br>124<br>124<br>125                                                                |

| <ul> <li>9.8.9 Special Character Detect Register</li> <li>9.8.10 Receive Mask</li> <li>9.9 ESCC DBDMA Channel Status Register Usage</li> <li>9.9.1 DBDMA Transmit Channel Status Register Usage</li> <li>9.9.2 DBDMA Receive Channel Status Register Usage</li> </ul>                                                                                                                                                                                                                                                                                               | 125<br>126<br>127<br>127<br>127                                                                       |

| <ul> <li>9.10 Conditional Interrupt, Branch and Wait Generation</li> <li>9.10.1 Transmit Channel</li> <li>9.10.2 Receive Channel</li> <li>9.10.3 Sending Packets Using the LTPC</li> <li>9.11 References</li> </ul>                                                                                                                                                                                                                                                                                                                                                 | 127<br>127<br>127<br>127<br>127<br>128                                                                |

| Chapter 10 Apple Desktop Bus Controller<br>10.1 CHRP Requirements<br>10.2 ADB Open Firmware Properties<br>10.3 ADB Registers<br>10.3.1 Interrupt Status (IST)<br>10.3.2 Command/Data Register File (CDRF)<br>10.3.3 Interrupt Source Enable (ISE)<br>10.3.4 Data Type Count (DTC)<br>10.5 Enable Status (ISD)                                                                                                                                                                                                                                                       | 129<br>129<br>129<br>130<br>131<br>131<br>132<br>132                                                  |

| 10.3.5       Error Status Register (ESR)         10.3.6       Control (CTL)         10.3.7       Autopoll Control (ACL)         10.3.8       Active Device Address High and Low (ACD)         10.4       CDRF Arbitration         10.5       Error Handling         10.5.1       Data Lost Error         10.5.2       No Response Error                                                                                                                                                                                                                             | 133<br>133<br>134<br>135<br>135<br>136<br>137<br>137                                                  |

| 10.5.3       SRQ Autopolling Error         10.5.4       Inactive Device Response Error         10.6       ADB Controller Special Functions         10.6.1       Keyboard-Invoked Reset or Interrupt         10.6.2       ADB Bus Reset         10.7       Timing Value         10.8       References                                                                                                                                                                                                                                                                | 137<br>138<br>138<br>138<br>139<br>139<br>139<br>140                                                  |

| Chapter 11 IDE Drive Controller<br>11.1 General Requirements<br>11.2 IDE Bus master Controller Open Firmware Properties<br>11.3 "Native-PCI" IDE Register Definition<br>11.4 Physical Region Descriptors for Bus master IDE<br>11.5 Bus Master IDE I/O Registers<br>11.5.1 Primary Command Register (PCR)<br>11.5.2 Secondary Command Register (SCR)<br>11.5.3 Primary Status Register (PSR)<br>11.5.4 Secondary Status Register (SSR)<br>11.5.5 Primary PRD Table Address Register (SPRD)<br>11.5.6 Secondary PRD Table Address Register (SPRD)<br>11.6 References | 141<br>141<br>142<br>142<br>143<br>143<br>143<br>143<br>144<br>144<br>145<br>145<br>145<br>146<br>146 |

#### Contents

| Chapter 12 SCSI                                 | 147          |

|-------------------------------------------------|--------------|

| 12.1 CHRP Requirements                          | 147          |

| 12.2 Overview and General Requirements          | 147          |

| 12.3 Mesh SCSI Open Firmware Properties         | 148          |

| 12.4 Interrupt Assignment                       | 149          |

| 12.5 MESH SCSI Register Definitions             | 149          |

| 12.5.1 Transfer Count 0 Register 0 (XferCount0) | 149          |

| 12.5.2 Transfer Count 1 Register (XferCount1)   | 150          |

| 12.5.3 Bus FIFO Register (FIFO)                 | 150          |

| 12.5.4 Sequence Register (Sequence)             | 150          |

| 12.5.5 Bus Status Register 0 (Status0)          | 153          |

| 12.5.6 Bus Status Register 1 (Status1)          | 153          |

| 12.5.7 Bus FIFO Count Register (FifoCount)      | 154          |

| 12.5.8 Exception Register (Exception)           | 154          |

| 12.5.9 Error Register (Error)                   | 155          |

| 12.5.10 Interrupt Mask Register                 | 155          |

| 12.5.11 Interrupt Register                      | 156          |

| 12.5.12 SourceID Register                       | 156          |

| 12.5.13 DestinationID Register                  | 156          |

| 12.5.14 SyncParms Register (SyncParms)          | 157          |

| 12.5.15 MESH ID Register (MeshID)               | 158          |

| 12.5.16 Selection TimeOut Register (SelTO)      | 158          |

| 12.6 DBDMA Registers                            | 158          |

| 12.7 References                                 |              |

| 12.7 Relefences                                 | 158          |

| Chapter 12 Craphics                             | 161          |

| Chapter 13 Graphics                             | 161          |

| 13.1 CHRP Requirements                          | 161          |

| 13.2 Bi-Endian Interface                        | 161          |

| 13.3 Linear Frame Buffer                        | 162          |

| 13.4 Video Graphics Array (VGA)                 | 162          |

| 13.5 References                                 | 162          |

| Chanter () / / / / / / / / / / / / / / / / / /  | 405          |

| Chapter 14 Versatile Interface Adapter (VIA)    | 165          |

| 14.1 CHRP Requirements                          | 165          |

| 14.2 VIA Open Firmware Requirements             | 165          |

| 14.3 Introduction                               | 165          |

| 14.3.1 Legacy Application                       | 165          |

| 14.3.2 Internal Timings                         | 166          |

| 14.4 VIA Registers                              | 166          |

| 14.4.1 Data Register B                          | 167          |

| 14.4.2 Data Register A                          | 168          |

| 14.4.3 Data Direction Register B                | 169          |

| 14.4.4 Data Direction Register A                | 169          |

| 14.4.5 Event Timers                             | 169          |

| 14.4.6 Shift Register                           | 169          |

| 14.4.7 Auxiliary Control Register               | 170          |

| 14.4.8 Peripheral Control Register              | 170          |

| 14.4.9 Interrupt Flag Register                  | 170          |

| 14.4.10 Interrupt Enable Register               | 170          |

| Chapter 15 Descriptor Deced DMA                 | A <b>7</b> 4 |

| Chapter 15 Descriptor-Based DMA                 | 171          |

| 15.1 Overview                                   | 171          |

| 15.2 DBDMA Characteristics                      | 171          |

| 15.3 Conventions                                | 172          |

| 15.4 Controller Registers                       | 173          |

| 15.4.1 Register Organization                    | 173          |

| 15.4.2 ChannelControl Register                  | 174          |

| 15.4.3 ChannelStatus Register                   | 174          |

| 15.4.4 CommandPtrLo Register                    | 176          |

xi

#### xii Contents

| 15.4.5 InterruptSelect Register                            | 176        |

|------------------------------------------------------------|------------|

| 15.4.6 BranchSelect Register                               | 177        |

| 15.4.7 WaitSelect Register                                 | 177        |

| 15.5 Summary of DBDMA Operations                           | 178        |

| 15.5.1 Multiplexed Channels                                | 178        |

| 15.5.2 Command-List Structure                              | 179        |

| 15.6 Design Model                                          | 180        |

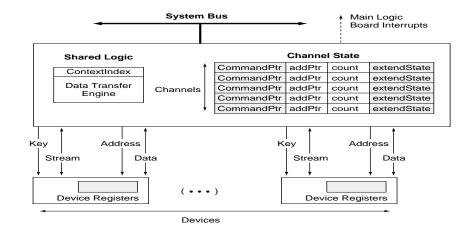

| 15.6.1 Controller Components                               | 180        |

| 15.6.2 System Bus Errors                                   | 181        |

| 15.6.3 Device Status                                       | 182        |

| 15.6.4 Conditional Actions                                 | 182        |

| 15.7 Commands                                              | 182        |

| 15.7.1 Command Formats<br>15.7.2 INPUT and OUTPUT Commands | 182<br>187 |

| 15.7.3 STORE_QUAD Command                                  | 187        |

| 15.7.4 LOAD_QUAD Command                                   | 188        |

| 15.7.5 NOP Command                                         | 189        |

| 15.7.6 STOP Command                                        | 190        |

| 15.8 Asynchronous Event Packet Formats                     | 190        |

| 15.9 Hardwired Interrupts                                  | 190        |

| 15.10 Examples                                             | 191        |

| 15.10.1 Command Queuing                                    | 191        |

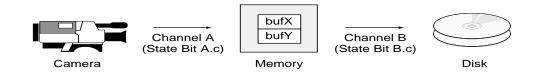

| 15.10.2 Ethernet Reception                                 | 192        |

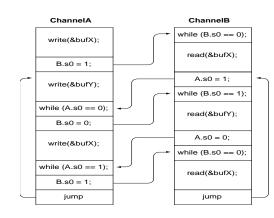

| 15.10.3 Full Handshake Flow Control                        | 193        |

|                                                            |            |

| Appendix A VGA Programming Model                           | 195        |

| A.1 Introduction                                           | 195        |

| A.2 VGA Modes                                              | 196        |

| A.2.1 Alphanumeric Modes                                   | 196        |

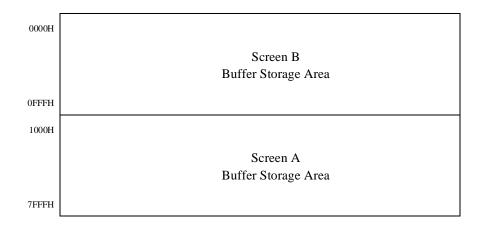

| A.2.2 Graphics Modes                                       | 198        |

| A.3 Registers                                              | 202        |

| A.3.1 General Registers                                    | 203        |

| A.3.2 Sequencer Registers                                  | 206        |

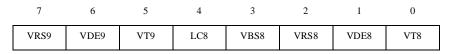

| A.3.3 CRT Controller Registers                             | 210        |

| A.3.4 Graphics Controller Registers                        | 221        |

| A.3.5 Attribute Controller Registers                       | 227        |

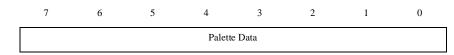

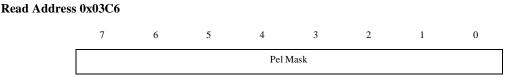

| A.3.6 Video Digital to Analog Converter                    | 231        |

| A.4 VGA Programming Considerations                         | 233        |

| A.4.1 Programming the Registers                            | 235        |

| A.4.2 RAM Loadable Character Generator                     | 236        |

| A.4.3 Creating a Split Screen                              | 236        |

| Appendix B Requirements Summary                            | 237        |

| Appendix B Requirements Summary                            | 201        |

| Glossary                                                   | 253        |

| Clobaly                                                    | 200        |

| Trademark Information                                      | 259        |

|                                                            |            |

| Bibliography                                               | 261        |

| Sources for Documents                                      | 263        |

| Obtaining Additional Information                           | 263        |

|                                                            |            |

| Index                                                      | 265        |

|                                                            |            |

# Figures

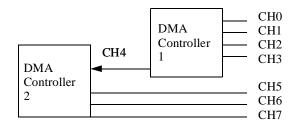

| 1.  | Cascaded DMA Controllers                            | 3   |

|-----|-----------------------------------------------------|-----|

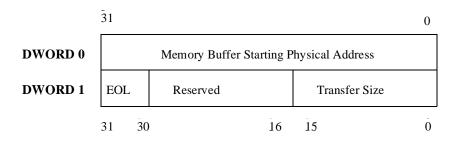

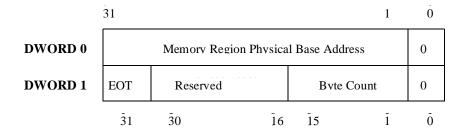

|     | Scatter Gather Descriptor Table Entry               | 26  |

| 3.  | PIC1 (master) and PIC2 (slave) Interconnection      | 61  |

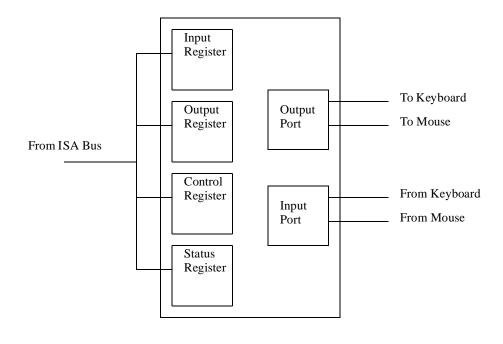

| 4.  | Block Diagram of Keyboard/Mouse Controller Register | 107 |

| 5.  | Physical Region Descriptors for Bus master IDE      | 143 |

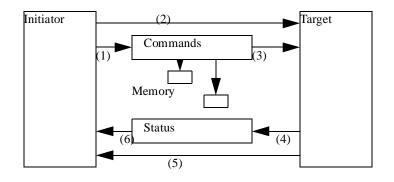

| 6.  | DBDMA Operation                                     | 178 |

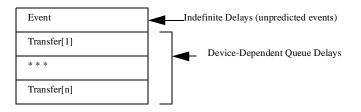

| 7.  | Multiplexed channel types                           | 179 |

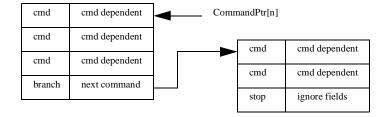

| 8.  | Command list structure                              | 180 |

| 9.  | DBDMA controller model                              | 181 |

| 10. | Flow-controlled device model                        | 193 |

| 11. | Synchronizing flow-controlled channel programs      | 194 |

| 12. | Character/Attribute Format                          | 197 |

# **Tables**

| i.   | Typographical Conventions                                              | xxvi  |

|------|------------------------------------------------------------------------|-------|

| ii.  | Register Characteristics                                               | xxvii |

| iii. | Minimum Requirements for Alphanumeric Input Device and Pointing Device | xxvii |

| 1.   | Summary of Minimum Requirements for ISA DMA (excerpt)                  | 3     |

| 2.   | Register Map for ISA DMA Device                                        | 5     |

| 3.   | Current Address Register 0 (CA0) Characteristics                       | 9     |

| 4.   | Current Address Register (CA0)                                         | 9     |

| 5.   | Base Address Register 0 (BA0) Characteristics                          | 10    |

| 6.   | Base Address Register (BA0)                                            | 10    |

| 7.   | Current Count Register 0 (CC0) Characteristics                         | 11    |

| 8.   | Current Count Register (CC0)                                           | 11    |

| 9.   | Base Count Register (BC0) Characteristics                              | 12    |

| 10.  | Base Count Register (BC0)                                              | 12    |

| 11.  | Current Low Page Register 0 (CLOP0) Characteristics                    | 12    |

| 12.  | Base Low Page Register 0 (BLOP0) Characteristics                       | 13    |

| 13.  | Current High Page Register 0 (CHIP0) Characteristics                   | 13    |

| 14.  | Base High Page Register 0 (BHIP0) Characteristics                      | 14    |

| 15.  | DMA 1 Command Register (DCOM1) Characteristics                         | 15    |

| 16.  | DMA Command Register                                                   | 15    |

| 17.  | DMA 2 Command Register (DCOM2) Characteristics                         | 16    |

| 18.  | DMA 1 Channel Mode Register (DCM1) Characteristics                     | 16    |

| 19.  | DMA Channel Mode Register                                              | 16    |

| 20.  | DMA 2 Channel Mode Register (DCM2) Characteristics                     | 17    |

| 21.  | DMA 1 Extended Mode Register (DCEM1) Characteristics                   | 17    |

| 22.  | DMA Extended Mode Register                                             | 17    |

| 23.  | DMA Timing Modes                                                       | 18    |

|      | DMA 2 Extended Mode Register (DCEM2) Characteristics                   | 19    |

|      | DMA 1 Request Register (DR1) Characteristics                           | 19    |

|      | DMA Request Register                                                   | 20    |

|      | DMA 2 Request Register (DR2) Characteristics                           | 20    |

| 28.  | DMA 1 Write Single Bit Mask Register (WSM1) Characteristics            | 20    |

| 29.  | DMA 1 Write Single Bit Mask Register                                   | 20    |

|      | DMA 2 Write Single Bit Mask Register (WSM2) Characteristics            | 21    |

|      | DMA 1 Write All Mask Register (WAM1) Characteristics                   | 21    |

|      | DMA 1 Write all Mask Bits Register                                     | 21    |

|      | DMA 2 Write All Mask Bits Register (WAM2) Characteristics              | 22    |

| 34.  | DMA 1 Status Register (DS1) Characteristics                            | 22    |

#### xvi Tables

| 35. | DMA 1 Status Register                                                       | 22     |

|-----|-----------------------------------------------------------------------------|--------|

|     | DMA 2 Status Register (DS2) Characteristics                                 | <br>23 |

|     | DMA 1 Clear Byte Pointer Register (CBP1) Characteristics                    | 23     |

|     | DMA 2 Clear Byte Pointer Register (CBP2) Characteristics                    | 24     |

|     | DMA 1 Master Clear Register (DMC1) Characteristics                          | 24     |

|     | DMA 2 Master Clear Register (DMC2) Characteristics                          | 24     |

|     | DMA 1 Clear Mask Register1 (DCLM1) Characteristics                          | 25     |

|     | DMA 2 Clear Mask Register (DCLM2) Characteristics                           | 25     |

|     | Scatter/Gather Interrupt Status Register (SGIS) Characteristics             | 26     |

|     | Scatter/Gather Interrupt Status Register (SGIS)                             | 27     |

|     | Scatter/Gather Command Register 0 (SGC0) Characteristics                    | 27     |

|     | Scatter/Gather Command Register 0 (SGC0)                                    | 27     |

|     | Scatter/Gather Commands                                                     | 27     |

|     | Scatter/Gather Status Register 0 (SGS0) Characteristics                     | 28     |

|     | Scatter/Gather Status Register 0 (SGS0)                                     | 28     |

|     | Scatter/Gather Descriptor Table Pointer Register 0 (SGPTR0) Characteristics | 29     |

|     | Summary of Minimum Platform Requirements                                    | 31     |

|     | Floppy Disk Controller Registers                                            | 33     |

|     | Status Register A (SRA) Characteristics                                     | 33     |

|     | Status Register A (SRA)                                                     | 33     |

|     | Status Register B (SRB) Characteristics                                     | 34     |

|     | Status Register B                                                           | 34     |

|     | Digital Output Register (DOR) Characteristics                               | 35     |

|     | Drive Control Register                                                      | 35     |

|     | Tape Drive Register (TDR) Characteristics                                   | 35     |

|     | Drive Status Register                                                       | 36     |

|     | Media ID Bit Functions                                                      | 36     |

|     | Tape Drive Assignment Values                                                | 36     |

|     | Main Status Register (MSR) Characteristics                                  | 37     |

|     | Diskette Drive Controller Status Register                                   | 37     |

|     | Data Rate Select Register (DRS) Characteristics                             | 37     |

|     | Precompensation Select Register                                             | 38     |

|     | Precompensation Values                                                      | 38     |

|     | Default Precompensation Values                                              | 38     |

|     | Data Rate Select Encodings                                                  | 39     |

|     | Data Register (FIFO) Characteristics                                        | 39     |

|     | Floppy FIFO Table                                                           | 40     |

|     | Digital Input Register (DIR) Characteristics                                | 40     |

|     | Diskette Drive Controller Status Register                                   | 40     |

|     | Configuration Control Register (CCR) Characteristics                        | 41     |

|     | Data Rate Control Register                                                  | 41     |

|     | Data Rate Selection                                                         | 41     |

|     | Autoeject Register (AEJ) Characteristics                                    | 41     |

|     | Configure Command Phase                                                     | 43     |

|     | Dumpreg Command Phase                                                       | 43     |

|     | Dumpreg Result Phase                                                        | 44     |

|     | Format Command Phase                                                        | 44     |

|     | Format Result Phase                                                         | 44     |

|     | Lock Command Phase                                                          | 45     |

|     | Lock Result Phase                                                           | 45     |

|     | Perpendicular Mode Command Phase                                            | 45     |

|     | Read Data Command Phase                                                     | 46     |

|     | Read Data Result Phase                                                      | 46     |

|     | Read Deleted Data Command Phase                                             | 46     |

|     | Read Deleted Data Result Phase                                              | 47     |

|     |                                                                             |        |

| 90.  | Read ID Command Phase                                             | 47 |

|------|-------------------------------------------------------------------|----|

| 91.  | Read ID Result Phase                                              | 47 |

| 92.  | Read Track Command Phase                                          | 48 |

| 93.  | Read Track Result Phase                                           | 48 |

| 94.  | Recalibrate Command Phase                                         | 48 |

| 95.  | Relative Seek Command Phase                                       | 49 |

| 96.  | Scan Equal Command Phase                                          | 49 |

|      | Scan Equal Result Phase                                           | 50 |

|      | Scan High or Equal Command Phase                                  | 50 |

|      | Scan High or Equal Result Phase                                   | 50 |

|      | Scan Low or Equal Command Phase                                   | 51 |

|      | Scan Low or Equal Result Phase                                    | 51 |

|      | Seek Command Phase                                                | 51 |

| 103. | Sense Drive Status Command Phase                                  | 52 |

| 104. | Sense Drive Status Result Phase                                   | 52 |

|      | Sense Interrupt Status Command Phase                              | 52 |

|      | Sense Interrupt Status Result Phase                               | 53 |

|      | Specify Command Phase                                             | 53 |

|      | Verify Command Phase                                              | 53 |

|      | Verify Result Phase                                               | 54 |

|      | Version Command Phase                                             | 54 |

| 111. | Version Result Phase                                              | 54 |

| 112. | Write Data Command Phase                                          | 54 |

| 113. | Write Data Result Phase                                           | 55 |

| 114. | Write Deleted Command Phase                                       | 55 |

| 115. | Write Deleted Result Phase                                        | 56 |

|      | Invalid Command Status Register                                   | 56 |

|      | Status Register 0                                                 | 56 |

|      | Encodings for the Interrupt Code field (bits 7,6 of ST0)          | 57 |

|      | Drive Select Bits                                                 | 57 |

|      | Status Register 1                                                 | 57 |

|      | Status Register 2                                                 | 58 |

|      | Status Register 3                                                 | 58 |

|      | Signal Connector Pin Assignment                                   | 59 |

|      | Minimum Platform Requirements for the Legacy Interrupt Controller | 61 |

|      | Legacy Interrupt Controller Registers                             | 63 |

|      | Interrupt Vector                                                  | 65 |

|      | Automatic Rotation Mode                                           | 66 |

|      | Specific Rotation Mode When IRQ5 Has the Lowest Priority          | 66 |

|      | Initialization Command Word 1 Register (ICW1) Characteristics     | 68 |

|      | Initialization Command Word 1 Register (ICW1)                     | 68 |

|      | Initialization Command Word 2 Register (ICW2) Characteristics     | 68 |

|      | Initialization Command Word 2 Register (ICW2)                     | 68 |

|      | Initialization Command Word 3 Register (ICW3) Characteristics     | 69 |

|      | Initialization Command Word 3 Register (ICW3)                     | 69 |

|      | Initialization Command Word 4 Register (ICW4) Characteristics     | 69 |

|      | Initialization Command Word 4 Register (ICW4)                     | 70 |

|      | Operation Command Word 1 Register (OCW1) Characteristics          | 70 |

|      | Operation Command Word 1 Register (OCW1)                          | 70 |

|      | OCW1 Bit Definitions                                              | 71 |

|      | Operation Command Word 2 Register (OCW2) Characteristics          | 71 |

|      | Operation Command Word 2 Register (OCW2)                          | 71 |

|      | Rotate and EOI Code                                               | 72 |

|      | Interrupt Level Select Encodings                                  | 72 |

|      | Operation Command Word 3Register (OCW3) Characteristics           | 72 |

|      |                                                                   |    |

#### xviii Tables

| 145 | Operation Command Word 3 Register (OCW3)                       | 73       |

|-----|----------------------------------------------------------------|----------|

|     | Interpretation of SMM and ESMM Bits                            | 73       |

|     | Register Read Command Decoding                                 | 73       |

|     | Interrupt Controller Response to a Read Pulse In Poll Mode     | 73       |

|     | Interrupt Request Register (IRR) Characteristics               | 74       |

|     | Interrupt Request Register (IRR)                               | 74       |

|     | In-Service Register (ISR) Characteristics                      | 75       |

|     | In-Service Register (ISR)                                      | 75       |

|     | Edge/Level Interrupt Control Register 1 (ELI1) Characteristics | 76       |

|     | Edge/Level Interrupt Control 1 Register (ELI1)                 | 76       |

|     | Edge/Level Interrupt Control 2 Register (ELI2) Characteristics | 76       |

|     | Edge/Level Interrupt Control 2 Register (ELI2)                 | 76       |

|     | Summary of the Parallel Port Controller Modes                  | 80       |

|     | Minimum Platform Requirements for the Parallel Port            | 80       |

|     | Parallel Port Controller Registers and Offsets                 | 83       |

|     | Data Register (DTR) Characteristics                            | 84       |

|     | Data Register (DTR)                                            | 84       |

|     | Status Register (STR or DSR) Characteristics                   | 85       |

|     | Status Register (STR or DSR)                                   | 85       |